数字信号处理器 QXS320C28x 指令手册

v2.3

合肥乾芯科技有限公司

## 表 1: 版本历史

| 版本号  | 日期         | 备注                                    |

|------|------------|---------------------------------------|

| 1.0  | 2019/06    | 初始版本                                  |

| 1.2  | 2020/03    | 增加VIL、VIH指令,修正部分指令功能描述错误              |

| 1.3  | 2020/04    | 修正部分指令功能描述错误                          |

| 1.4  | 2021/09    | 增加浮点矢量运算指令                            |

| 1.5  | 2022/03    | 依流片版本信息更新文档                           |

| 1.6  | 2022/06    | 更新C2000-3槽指令                          |

| 1.7  | 2024/09    | 添加VCU指令                               |

| 1.8  | 2024/10    | 添加部分64位指令                             |

| 1.12 | 2024/12    | 修正MUL64指令行为、修正FSEQ指令语法、更新TMU指令说明、删除未实 |

|      |            | 现的指令                                  |

| 2.0  | 2025/05/27 | 添加v2内核内容                              |

| 2. 1 | 2025/06/24 | 添加INTR指令说明                            |

| 2. 2 | 2025/08/19 | 添加v3内核说明及指令                           |

| 2. 3 | 2025/08/26 | 区分部分TMU指令的v1/v2版本                     |

# 目 录

| 1. | 概述              | 10                  |

|----|-----------------|---------------------|

| 2. | VLIW 槽定义        | 11                  |

| 3. | · 寄存器说明         | 11                  |

|    | 3.1. 寄存器堆描述     |                     |

|    |                 | Control Register)12 |

|    |                 | 12                  |

|    | 3.2.2. v2/v3 内核 | 12                  |

|    | 3.3. 中断返回地址寄有   | E器(ICA)12           |

|    | 3.4. 通用寄存器使用惯   | [初]                 |

| 4. | . 基础指令          | 14                  |

|    | 4.1. 特殊指令       | 14                  |

|    | 4.1.1. NOP      | 14                  |

|    | 4.1.2. IDLE     | 15                  |

|    | 4.1.3. EALLOW   |                     |

|    | 4.1.4. EDIS     |                     |

|    | 4.1.5. SETCINTM | 20                  |

|    |                 | 21                  |

|    | 4.2. 控制流指令      | 22                  |

|    |                 | 22                  |

|    |                 | 23                  |

|    |                 | 24                  |

|    |                 | 25                  |

|    |                 | 26                  |

|    |                 | 27                  |

|    |                 | 28                  |

|    |                 | 29                  |

|    |                 | 30                  |

|    |                 |                     |

|    |                 | 32                  |

|    |                 |                     |

|    |                 | 34                  |

|    |                 | 35                  |

|    |                 | 36                  |

|    |                 | 37                  |

|    |                 | 38                  |

|    |                 | 39                  |

|    |                 | 40                  |

|    | 4.2.20. INTR    | 41                  |

|      | 4.2.21.  | IACK        | 42 |

|------|----------|-------------|----|

| 4.3. | 数据       | 传送指令        | 43 |

|      | 4.3.1. N | MOVIGH      | 43 |

|      | 4.3.2. N | MOVIGL      | 44 |

|      | 4.3.3. N | MOVG2G      | 45 |

|      | 4.3.4. N | MOVG2C      | 46 |

|      | 4.3.5. N | MOVC2G      | 47 |

|      | 4.3.6. N | MOVIGLZ     | 48 |

|      | 4.3.7. N | MOVIGLX     | 49 |

| 4.4. | 加载       | /存储指令       | 50 |

|      | 4.4.1. L | .OAD8       | 50 |

|      | 4.4.2. L | OAD16       | 51 |

|      | 4.4.3. L | .OAD32      | 52 |

|      | 4.4.4.   | STORE8      | 53 |

|      | 4.4.5.   | STORE16     | 54 |

|      | 4.4.6.   | STORE32     | 55 |

|      |          | .OADU8      |    |

|      |          | OADU16      |    |

|      | 4.4.9. L | OADU32      |    |

|      | 4.4.10.  | STOREU8     |    |

|      | 4.4.11.  | STOREU16    | 60 |

|      | 4.4.12.  | STOREU32    |    |

|      | 4.4.13.  | LOADO16     |    |

|      | 4.4.14.  | LOADO32     |    |

|      | 4.4.15.  | STOREO16    |    |

|      | 4.4.16.  | STOREO32    | 65 |

|      | 4.4.17.  | LOADI8      | 66 |

|      | 4.4.18.  | LOADI16     | 67 |

|      | 4.4.19.  | LOADI32     | 68 |

|      | 4.4.20.  | STOREI8     | 69 |

|      | 4.4.21.  | STOREI16    | 70 |

|      | 4.4.22.  | STOREI32    | 71 |

| 4.5. | 标量       | 运算指令 – 比较指令 | 72 |

|      |          | EQI         |    |

|      | 4.5.2. N | NEQI        | 73 |

|      | 4.5.3.   | GTI         | 74 |

|      | 4.5.4. L | .TI         | 75 |

|      | 4.5.5.   | GEI         | 76 |

|      | 4.5.6. L | .EI         | 77 |

|      | 4.5.7. E | EQ          | 78 |

|      |          | NEQ         |    |

|      | 4.5.9.   | 3T          | 80 |

|      | 4.5.10.    |            | 81  |

|------|------------|------------|-----|

|      | 4.5.11.    | GE         | 82  |

|      | 4.5.12.    | LE         | 83  |

|      | 4.5.13.    | GTU        | 84  |

|      | 4.5.14.    | LTU        | 85  |

|      | 4.5.15.    | GEU        | 86  |

|      | 4.5.16.    | LEU        | 87  |

|      | 4.5.17.    | TEST       | 88  |

|      | 4.5.18.    | TESTI      | 89  |

|      | 4.5.19.    | EQU        | 90  |

|      | 4.5.20.    | NEQU       | 91  |

|      | 4.5.21.    | EQIU       | 92  |

|      | 4.5.22.    | NEQIU      | 93  |

|      | 4.5.23.    | GTIU       | 94  |

|      | 4.5.24.    | LTIU       | 95  |

|      | 4.5.25.    | GEIU       | 96  |

|      | 4.5.26.    | LEIU       | 97  |

| 4.6. | 标量运        | 算指令 – 运算指令 | 98  |

|      | 4.6.1. ADI | DI         | 98  |

|      | 4.6.2. ADI | DIC        | 99  |

|      | 4.6.3. ADI | O          | 100 |

|      | 4.6.4. ADI | DC         | 101 |

|      | 4.6.5. SUE | 3          | 102 |

|      | 4.6.6. SUE | 3C         | 103 |

|      | 4.6.7. MU  | L32        | 104 |

|      | 4.6.8. MU  | L64        | 105 |

|      | 4.6.9. MU  | LU32       | 106 |

|      | 4.6.10.    | MAX        | 107 |

|      | 4.6.11.    | MIN        | 108 |

|      | 4.6.12.    | ABS        | 109 |

|      | 4.6.13.    | CBW        | 110 |

|      | 4.6.14.    | CHW        | 111 |

|      | 4.6.15.    | SAT64      | 112 |

|      | 4.6.16.    | NEG        | 113 |

|      | 4.6.17.    | SUBI       | 114 |

|      | 4.6.18.    | SUBIC      | 115 |

|      | 4.6.19.    | SELECT     | 116 |

|      | 4.6.20.    | SETC       | 117 |

|      | 4.6.21.    | MULU64     | 118 |

|      | 4.6.22.    | MAC16      | 119 |

|      | 4.6.23.    | MACU16     | 120 |

|      | 4.6.24.    | MAC32      | 121 |

|    |      | 4.6.25. | MAC64   | 122       |

|----|------|---------|---------|-----------|

|    |      | 4.6.26. | MACU32. | 123       |

|    |      | 4.6.27. | MACU64. | 124       |

|    | 4.7. | 标量      | ≣运算指令 − | 逻辑指令125   |

|    |      | 4.7.1.  | AND     | 125       |

|    |      | 4.7.2.  | OR      | 126       |

|    |      | 4.7.3.  | XOR     | 127       |

|    |      | 4.7.4.  | NOT     | 128       |

|    |      | 4.7.5.  | SL      | 129       |

|    |      | 4.7.6.  | SRA     | 130       |

|    |      | 4.7.7.  | SRL     | 131       |

|    |      | 4.7.8.  | NEG64   | 132       |

|    |      | 4.7.9.  | SRA64   | 133       |

|    |      | 4.7.10. | SL64    | 134       |

|    |      | 4.7.11. | SRL64   | 135       |

|    |      | 4.7.12. | SLI     | 136       |

|    |      | 4.7.13. | SRAI    | 137       |

|    |      | 4.7.14. |         |           |

|    | 4.8. | 标量      | 量运算指令 − | 比特位域指令139 |

|    |      |         |         |           |

|    |      | 4.8.2.  | BFEXTU  |           |

|    |      |         |         |           |

|    |      |         |         |           |

|    |      | 4.8.5.  | BCLR    | 143       |

| 5. | FPU  | 指令      |         | 144       |

|    | 5 1  | 运售      | 争指今     | 144       |

|    | 3.1. |         |         |           |

|    |      |         |         |           |

|    |      | _       |         | 146       |

|    |      |         |         | 147       |

|    |      |         | •       | 148       |

|    |      |         |         | 149       |

|    |      |         | -       |           |

|    |      | 5.1.8.  | FSSUB   |           |

|    |      | 5.1.9.  | FSABS   |           |

|    |      | 5.1.10. | FSMAX   | 153       |

|    |      | 5.1.11. |         | 154       |

|    |      | 5.1.12. |         | 155       |

|    |      | 5.1.13. |         | 156       |

|    |      | 5.1.14. |         | 157       |

|    |      | 5.1.15. |         | 158       |

|    |      |         |         |           |

|    |      | 5.1.16. | FDABS      | 159 |

|----|------|---------|------------|-----|

|    |      | 5.1.17  | FDMAX      | 160 |

|    |      | 5.1.18. | FDMIN      | 161 |

|    | 5.2. | 比车      | 交指令        | 162 |

|    |      | 5.2.1.  | FSEQ       | 162 |

|    |      | 5.2.2.  | FSGT       | 163 |

|    |      | 5.2.3.  | FSLT       | 164 |

|    |      | 5.2.4.  | FSGE       | 165 |

|    |      | 5.2.5.  | FSLE       | 166 |

|    |      | 5.2.6.  | FDEQ       | 167 |

|    |      | 5.2.7.  | FDGT       | 168 |

|    |      | 5.2.8.  | FDLT       | 169 |

|    |      | 5.2.9.  | FDGE       | 170 |

|    |      | 5.2.10. | FDLE       | 171 |

|    | 5.3. | 类型      | 2转换指令      | 172 |

|    |      | 5.3.1.  | FCVTSF     | 172 |

|    |      |         | FCVTFS     |     |

|    |      |         | FCVTSU     |     |

|    |      |         | FCVTUS     |     |

|    |      |         | FCVTDF     |     |

|    |      | 5.3.6.  | FCVTFD     | 177 |

|    |      |         | FCVTDU     | _   |

|    |      |         | FCVTUD     |     |

|    |      |         | FCVTDS     |     |

|    |      | 5.3.10. | FCVTSD     | 181 |

| 6. | TMU  | 指令      |            | 182 |

|    | 6.1. | MP      | Y2PIF32    | 182 |

|    | 6.2. | DIV     | /2PIF32    | 183 |

|    | 6.3. | SIN     | IPUF32.v1  | 184 |

|    | 6.4. | SIN     | IPUF32.v2  | 185 |

|    | 6.5. | CO      | SPUF32     | 186 |

|    | 6.6. | ATA     | ANPUF32.v1 | 187 |

|    | 6.7. | ATA     | ANPUF32.v2 | 188 |

|    | 6.8. | QU      | ADF        | 189 |

|    | 6.9. | EX      | PPUF32     | 191 |

|    | 6.10 | ). LO   | GPUF32     | 192 |

| 7. | VCU  | 指令      |            | 193 |

|    | 7.1. | VS      | TATUS 寄存器  | 193 |

|    |      |         | 配置方法       |     |

|    |      |         | 寄存器定义      |     |

|    | 7.2. |         | 文指令        |     |

|    |      |         |            |     |

|      | 7.2.1. VCADD       | .194 |

|------|--------------------|------|

|      | 7.2.2. VCSUB       | .196 |

|      | 7.2.3. VCDA16      | .197 |

|      | 7.2.4. VCDS16      | .199 |

|      | 7.2.5. VNEG        | .201 |

|      | 7.2.6. VCMPY       | .202 |

|      | 7.2.7. VCMPYAC     | .203 |

| 7.3. | CRC 指令             | .205 |

|      | 7.3.1. VCRC8LL     | .205 |

|      | 7.3.2. VCRC8LH     | .206 |

|      | 7.3.3. VCRC8HL     | .207 |

|      | 7.3.4. VCRC8HH     | .208 |

|      | 7.3.5. VCRC16P1LL  | .209 |

|      | 7.3.6. VCRC16P1LH  | .210 |

|      | 7.3.7. VCRC16P1HL  | .211 |

|      | 7.3.8. VCRC16P1HH  | .212 |

|      | 7.3.9. VCRC16P2LL  | .213 |

|      | 7.3.10. VCRC16P2LH | .214 |

|      | 7.3.11. VCRC16P2HL | .215 |

|      | 7.3.12. VCRC16P2HH |      |

|      | 7.3.13. VCRC32LL   | .217 |

|      | 7.3.14. VCRC32LH   | .218 |

|      | 7.3.15. VCRC32HL   | .219 |

|      | 7.3.16. VCRC32HH   | .220 |

| 7.4. | Viterbi 指令         |      |

|      | 7.4.1. VITBM2      | .221 |

|      | 7.4.2. VITBM3      | .222 |

|      | 7.4.3. VITDHAS     | .224 |

|      | 7.4.4. VITDHSA     | .225 |

|      | 7.4.5. VITDLAS     | .226 |

|      | 7.4.6. VITDLSA     | .227 |

|      | 7.4.7. VITHSEL     | .228 |

|      | 7.4.8. VITLSEL     | .230 |

|      | 7.4.9. VTCLEAR     | .232 |

|      | 7.4.10. VTRACE     | .233 |

| 7.5. | Viterbi II 指令      | .235 |

|      | 7.5.1. VDEC        | .235 |

|      | 7.5.2. VINC        | .236 |

|      | 7.5.3. VCCON       | .237 |

|      | 7.5.4. VCFLIP      | .238 |

|      | 7.5.5. VCSHL       | .239 |

|      | 7.5.6. VCSHR       | .240 |

| 7.5.7.  | VCMAG      | 241 |

|---------|------------|-----|

| 7.5.8.  | VCRC24LL   | 242 |

| 7.5.9.  | VCRC24LH   | 243 |

| 7.5.10. | VCRC24HL   | 244 |

| 7.5.11. | VCRC24HH   | 245 |

| 7.5.12. | VCRC32P2LL | 246 |

| 7.5.13. | VCRC32P2LH | 247 |

| 7.5.14. | VCRC32P2HL | 248 |

| 7.5.15. | VCRC32P2HH | 249 |

| 7.5.16. | VCFFT1     | 250 |

| 7.5.17. | VCFFT6     | 252 |

| 7.5.18. | VCFFT8     | 254 |

| 7.5.19. | VCFFT9     | 256 |

| 7.5.20. | VCFFT10    | 258 |

| 7.5.21. | VGFACC     | 260 |

| 7.5.22. | VGFADD     | 261 |

| 7.5.23. | VREVB      | 263 |

| 7.5.24. | VPACK      | 264 |

| 7.5.25. | VGFMPY     | 265 |

| 7.5.26. | VGFMAC     | 266 |

| 7.5.27. | VSHLMB     | 267 |

# 1. 概述

本文档为 QXS320C28x 指令手册, 描述处理器指令及指令功能。

目前,QXS320C28x内核有三个迭代版本:

v1: 2024 年量产

v2: 2025 年量产

- 在 v1 内核的基础上新增指令

- 扩充控制寄存器(CR)定义

v3: 2025 年量产

- 在 v2 内核的基础上新增双精度浮点指令 和 CLA 任务触发指令 当前基于 QXS320C28x 内核的微控制器型号及内核版本如表 2 所示。

| 索引 | 微控制器              | 内核版本 |

|----|-------------------|------|

| 1  | QXS320F280049RevA | v1   |

| 2  | QXS320F28377LRevA | VI   |

| 3  | QXS320F280049RevB |      |

| 4  | QXS320F28377LRevB | v2   |

| 5  | QXS320F2800137    | V2   |

| 6  | QXS320F28034      |      |

| 7  | QXS320F28P650     | v2   |

| 8  | QXS320F28377D     | v3   |

表 2: 微控制器及内核版本

# 2. VLIW 槽定义

QXS320C28x 采用 VLIW 结构,并包含 3 个指令槽(slot0、slot1、slot2),每个指令槽可以容纳一条指令。每个 VLIW 可能包含的指令数量为 1~3,对应 VLIW 指令长度可能为 32~96 位。

每个槽能容纳的指令类型为:

Slot0: 特殊指令、控制流指令、数据传送指令、标量运算指令、FPU/TMU/VCU 指令

Slot1: NOP、加载指令

Slot2: NOP、存储指令

# 3. 寄存器说明

## 3.1. 寄存器堆描述

| 标记  | 名称    | 宽度 | 数量 |

|-----|-------|----|----|

| GR  | 通用寄存器 | 32 | 32 |

| OFF | 偏移寄存器 | 32 | 4  |

| BAR | 基址寄存器 | 32 | 4  |

| MR  | 取模寄存器 | 32 | 4  |

## 3.2. 控制寄存器 (CR: Control Register)

#### 3.2.1. v1 内核

CR 可以通过 MOVG2C、MOVC2G 进行设置及保存

- [13:12]OVF: 溢出标志位, 10/11/00 三种情况对应上/下/无溢出。

- [7] OF: 溢出标志位,产生溢出,该标志位设置为 1,否则设置为 0。

- [4] CON: 标量比较指令的结果,如果比较结果成立则该标志位设置为 1,否则设置为 0;如果当前不是比较指令,则该标志位保持不变。CR[4]对应 slot0。

- [0] CF: 标量运算的最高位是否产生进位/借位, CR [0]对应 slot0。

### 3.2.2. v2/v3 内核

CR 可以通过 MOVG2C、MOVC2G 进行设置及保存

- [14]EALLOW: 系统中的一些寄存器被 EALLOW 保护机制保护, 防止伪 CPU 写入。

- [13:12]OVF: 溢出标志位, 10/11/00 三种情况对应上/下/无溢出。

- [7] OF: 溢出标志位,产生溢出,该标志位设置为 1,否则设置为 0。

- [4] CON: 标量比较指令的结果,如果比较结果成立则该标志位设置为 1,否则设置为 0;如果当前不是比较指令,则该标志位保持不变。CR[4]对应 slot0。

- [2]LVF FPU/TMU 上溢

- [1]LUF FPU/TMU 下溢

- [0] CF: 标量运算的最高位是否产生进位/借位, CR [0]对应 slot0。

## 3.3. 中断返回地址寄存器(ICA)

保存中断返回的地址,为特殊寄存器。寄存器地址为: 0x007F0718。

# 3.4. 通用寄存器使用惯例

| 通用寄存器 | 使用惯例                       | caller/callee-saved |

|-------|----------------------------|---------------------|

| GR0   | 中断向量表基地址                   | n/a                 |

| GR1   | 通用寄存器                      | n/a                 |

| GR2   | 传递函数返回值                    |                     |

| GR3   | 传递函数返回值(64bit 返回值的高 32bit) |                     |

| GR4   | 传递函数第一个实参                  |                     |

| GR5   | 传递函数第二个实参                  |                     |

| GR6   | 传递函数第三个实参                  |                     |

| GR7   | 传递函数第四个实参                  |                     |

| GR8   | 通用寄存器                      | caller-saved        |

| GR9   | 通用寄存器                      | Caller-Saveu        |

| GR10  | 通用寄存器                      |                     |

| GR11  | 通用寄存器                      |                     |

| GR12  | 通用寄存器                      |                     |

| GR13  | 通用寄存器                      |                     |

| GR14  | 通用寄存器                      |                     |

| GR15  | 通用寄存器                      |                     |

| GR16  | 通用寄存器                      |                     |

| GR17  | 通用寄存器                      |                     |

| GR18  | 通用寄存器                      |                     |

| GR19  | 通用寄存器                      | callee-saved        |

| GR20  | 通用寄存器                      | Callee-Saveu        |

| GR21  | 通用寄存器                      |                     |

| GR22  | 通用寄存器                      |                     |

| GR23  | 通用寄存器                      |                     |

| GR24  | 通用寄存器                      |                     |

| GR25  | 通用寄存器                      |                     |

| GR26  | 通用寄存器                      | caller-saved        |

| GR27  | 通用寄存器                      |                     |

| GR28  | 通用寄存器                      |                     |

| GR29  | 通用寄存器                      | callee-saved        |

| GR30  | 栈指针 (SP)                   | n/a                 |

| GR31  | 函数返回地址(LR)                 | callee-saved        |

# 4. 基础指令

## 4.1. 特殊指令

## 4.1.1. NOP

内核: v1

格式:

NOP

目的:

空操作

#### 描述:

不执行任何操作,不影响寄存器值和处理器状态。

## 限制条件:

;

操作:

•

异常:

:

备注:

;

#### 4.1.2. IDLE

内核: v1

格式:

**IDLE**

目的:

进入低功耗模式

#### 描述:

有三种低功耗模式,IDLE、STANDBY、HALT,三种低功耗模式通过 IDLE 指令进行进

入,低功耗模式的种类通过 LPMCR 寄存器进行配置。

#### 限制条件:

#### 操作:

IDLE 是 C2000 CPU 的标准功能。在这种模式下,CPU 时钟是门控的,而所有外围时钟都保持运行。因此,IDLE 可以用于在 CPU 等待外设事件时节省 power。

任何启用的中断都会将 CPU 从 IDLE 模式唤醒。

- 1.设置 LPMCR, LPM 到 0x0 并执行 IDLE 指令,则进入到 IDLE MODE。

- 2.当被启用中断事件发生时,进入到 IDLE\_EXIT 状态,如果此时无 IDLE 指令,则进入 NORMAL,若中断未被屏蔽则会进入中断,否则 CPU 将恢复正常的操作。

STANDBY 是一种更激进的低功耗模式,它对 CPU 时钟和从 CPU 的 SYSCLK 派生的任何外设时钟进行门控,看门狗仍可处于 Active 状态,其他 CPU 子系统及其所有外设会被同步控制进入低功耗。STANDBY 最适合唤醒信号来自外部系统而不是外设输入的应用,看门狗中断(可选),GPIOO-63 中的任何一个可以被配置为在它们被驱动为低驱动时唤醒 CPU 子系统。在唤醒时,CPU 接收 WAKEINT 中断。

要进入 STANDBY 模式: (不包含 flash 和 pll 相关)

- 1.将 LPMCR.LPM 设置为 0x1。

- 2.启用 PIE 中的 WAKEINT 中断。

- 3.对于看门狗中断唤醒,将 LPMCR.WDINTE 设置为 1,并配置看门狗以生成中断。

- 4.对于 GPIO 唤醒,设置 GPIOLPMSELO 和 GPIOLPMSEL1 以将所选 GPIO 连接到 LPM 模块。

- 5.执行 IDLE 指令。。

#### 要从 STANDBY 模式唤醒:

- 1.配置所需的 GPIO 以触发唤醒。

- 2.将所选 GPIO 低电平驱动至少 5us,这将激活 WAKEINT PIE 中断; WAKEINT 中断被锁存在 PIE 块中。WAKEINT 中断也可以由看门狗中断触发。

- 3. 若此时无 IDLE 指令,则退出低功耗模式进入 NORMAL 状态,执行 WAKEINT 中断,芯片开始正常工作。

CPU 现在已脱离 STANDBY 模式,可以恢复正常执行。

HALT 是一种全局低功耗模式,几乎可以门控所有系统时钟,并允许 XTAL 和模拟块断电。与其他 C2000 设备不同,HALT 模式不会在进入 HALT 时自动关闭 XTAL。

对于在 HALT 模式期间的最小功耗,应用程序软件应在进入 HALT 之前关闭 XTAL。如果 OSCCLK 源配置为 XTAL,则在设置 XTALCR.OSCOFF 之前,应用程序应首先将 OSSCLK 源切换到 INTOSC1 或 INTOSC2。

GPIO0-63 可以配置为从 HALT 唤醒系统,且没有其他唤醒选项可用。在唤醒时, CPU 接收 WAKEINT 中断。

#### 要进入 HALT 模式:

- 1.启用 PIE 中的 WAKEINT 中断。

- 2.将 LPMCR.LPM 设置为 0x2。设置 GPIOLPMSEL0 和 GPIOLPMSEL1,将所选 GPIO 连接到 LPM 模块。

- 3.将 CLKSRCCTL1.WDHALTI 设置为 1,以保持看门狗定时器处于活动状态,并且 INTOSC1 和 INTOSC2 在 HALT 中通电。

- 4.将 CLKSRCCTL1.WDHALTI 设置为 0 以禁用看门狗定时器,并在 HALT 中关闭 INTOSC1 和INTOSC2。

5.执行 IDLE 指令以进入 HALT 模式。

## 要从 HALT 模式唤醒:

- 1.将所选 GPIO 低电平驱动至少 5us,这将激活 WAKEINT PIE 中断。

- 2.再次驱动唤醒 GPIO 为高电平,以启动 SYSPLL 的加电。

- 3.等待 16us 加 1024 个 OSCCLK 周期,以允许 PLL 锁定和 WAKEINT ISR 锁定。

- 4.执行 WAKEINT ISR。

## 异常:

#### 备注:

## **4.1.3. EALLOW**

内核: v2

格式:

**EALLOW**

目的:

打开对外设写寄存器的控制

描述:

将控制寄存器中 eallow 控制位置 1

限制条件:

操作:

cpu\_ctrlReg[14] ← 1

异常:

备注:

;

## 4.1.4. EDIS

内核: v2

格式:

EDIS

目的:

关闭对外设写寄存器的控制

描述:

将控制寄存器中 eallow 控制位置 0

限制条件:

操作:

cpu\_ctrlReg[14] ← 0

异常:

备注:

•

## **4.1.5. SETCINTM**

内核: v2

格式:

SETCINTM

目的:

屏蔽全体外设中断

描述:

作用同向 intm 寄存器写 1

限制条件:

;

操作:

异常:

;

备注:

;

## **4.1.6. CLRCINTM**

内核: v2

格式:

CLRCINTM

目的:

解除屏蔽全体外设中断

描述:

作用同向 intm 寄存器写 0

限制条件:

;

操作:

异常:

;

备注:

:

## 4.2. 控制流指令

## 4.2.1. JMP

内核: v1

格式:

JMP addr<sub>21</sub>

目的:

无条件相对跳转到目标地址。

### 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

## 限制条件:

imm 为 21 位立即数

操作:

PC **←** PC + addr << 2

异常:

备注:

有两个延迟槽, 由编译器填充指令

## 4.2.2. JC

内核: v1

格式:

JC addr<sub>21</sub>

目的:

满足条件则相对跳转到目标地址。

## 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

#### 限制条件:

imm 为 21 位立即数

## 操作:

**IF** CON

PC ← PC + addr << 2

异常:

. .

备注:

有两个延迟槽,由编译器填充指令

## 4.2.3. JNC

内核: v1

格式:

JNC addr<sub>21</sub>

目的:

不满足条件则相对跳转到目标地址。

## 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

#### 限制条件:

imm 为 21 位立即数

## 操作:

IF ~CON

PC ← PC + addr << 2

异常:

备注:

有两个延迟槽,由编译器填充指令

## 4.2.4. CALL

内核: v1

格式:

CALL addr<sub>21</sub>

目的:

调用子程序。

#### 描述:

目的地址的有效范围: 当前 PC + [-4MB, 4MB-4B], 地址偏移由 21-bit 的 addr 左移 2

bit 产生。当前 PC+8(CALL\_PC + 12)保存到 GR[31](Link Register)

#### 限制条件:

imm 为 21 位有符号立即数

#### 操作:

GR[31] ← PC + 8

PC ← PC + addr << 2

## 异常:

;

#### 备注:

有两个延迟槽, 由编译器填充指令

25

## 4.2.5. **JMPR**

内核: v1

格式:

JMPR Rs

目的:

无条件绝对跳转到目标地址。

描述:

目标地址为 Rs 中的数。

限制条件:

Rs 为 GR

操作:

PC **←** Rs

异常:

;

备注:

有两个延迟槽,由编译器填充指令

## 4.2.6. CALLR

内核: v1

格式:

**CALLR Rs**

目的:

调用子程序。

## 描述:

子程序地址为 Rs 中的数据。调用目标地址处的子程序,将当前 PC 保存在 GR[31] (Link

Register)中,以便于跳出子程序

## 限制条件:

Rd 为 GR

操作:

GR[31] **←** PC+8

PC **←** Rs

异常:

:

备注:

有两个延迟槽, 由编译器填充指令

## 4.2.7. **RET**

内核: v1

格式:

RET

目的:

子程序返回。

## 描述:

返回的目的地址为 GR[31](Link Register)中的内容。

## 限制条件:

;

操作:

PC **←** GR[31]

异常:

;

备注:

有两个延迟槽,由编译器填充指令

## 4.2.8. RTT

内核: v1

格式:

RTT

目的:

中断返回。

描述:

返回的目的地址为中断地址寄存器 ICA 的内容

限制条件:

;

操作:

PC ← ICA

异常:

;

备注:

有两个延迟槽,由编译器填充指令

## 4.2.9. LOOP

内核: v1

#### 格式:

LOOP Rd, addr<sub>16</sub>

#### 目的:

循环。

#### 描述:

循环次数为 Rd 值加一,循环出口地址 loop end 为地址标签(addr),即循环体最后一条指令地址。loopbegin 由硬件生成。每次在执行到循环体最后一条指令的时候,判断 loop counter 是否为 0,如果是则跳出循环至 loop end,如果不是则跳回 loop begin 重新执行循环体。

#### 限制条件:

Rd 为 GR, addr 为 16 位立即数

## 操作:

loopend ← PC + addr << 2

loopcounter ← Rd

#### 异常:

;

#### 备注:

;

## 4.2.10. SYNCH

内核: v1

格式:

SYNCH

目的:

同步操作

描述:

限制条件:

;

操作:

异常:

;

备注:

•

## 4.2.11. TRAP

内核: v1

格式:

TRAP imm<sub>18</sub>

目的:

用于调试的自陷指令

描述:

遇到 TRAP 后,处理器暂停,将 imm 送至 debug 模块的 DRR 寄存器

限制条件:

操作:

异常:

;

备注:

;

## 4.2.12. SJMP

内核: v2

格式:

SJMP addr<sub>21</sub>

目的:

无条件相对跳转到目标地址。

## 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

#### 限制条件:

imm 为 21 位立即数

操作:

PC **←** PC + addr << 2

异常:

备注:

该跳转指令不具有延迟槽;

## 4.2.13. SJC

内核: v2

格式:

SJC addr<sub>21</sub>

目的:

满足条件则相对跳转到目标地址。

## 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

#### 限制条件:

imm 为 21 位立即数

操作:

**IF** CON

PC ← PC + addr << 2

异常:

备注:

该跳转指令不具有延迟槽;

34

## 4.2.14. SJNC

内核: v2

格式:

SJNC addr<sub>21</sub>

目的:

不满足条件则相对跳转到目标地址。

## 描述:

地址的有效范围是当前的 8M(2<sup>21+2</sup>B)区域。相对地址由 21 位的 Addr 域左移 2 位产生。

#### 限制条件:

imm 为 21 位立即数

操作:

IF ~CON

PC ← PC + addr << 2

异常:

备注:

该跳转指令不具有延迟槽;

## 4.2.15. SCALL

内核: v2

格式:

SCALL addr<sub>21</sub>

目的:

调用子程序。

#### 描述:

目的地址的有效范围: 当前 PC + [-4MB, 4MB-4B], 地址偏移由 21-bit 的 addr 左移 2

bit 产生。当前 PC+8(CALL\_PC + 12)保存到 GR[31](Link Register)

#### 限制条件:

imm 为 21 位有符号立即数

#### 操作:

GR[31] ← PC + 8

PC ← PC + addr << 2

异常:

#### 备注:

该跳转指令不具有延迟槽;

### 4.2.16. SJMPR

内核: v2

格式:

SJMPR Rs

目的:

无条件绝对跳转到目标地址。

描述:

目标地址为 Rs 中的数。

限制条件:

Rs 为 GR

操作:

PC **←** Rs

异常:

,

备注:

### 4.2.17. SCALLR

内核: v2

格式:

**SCALLR Rs**

目的:

调用子程序。

### 描述:

子程序地址为 Rs 中的数据。调用目标地址处的子程序,将当前 PC 保存在 GR[31] (Link

Register)中,以便于跳出子程序

### 限制条件:

Rd 为 GR

操作:

GR[31] **←** PC+8

PC **←** Rs

异常:

;

备注:

### 4.2.18. SRET

内核: v2

格式:

SRET

目的:

子程序返回。

### 描述:

返回的目的地址为 GR[31](Link Register)中的内容。

### 限制条件:

;

操作:

PC **←** GR[31]

异常:

;

备注:

### 4.2.19. SRTT

内核: v2

格式:

SRTT

目的:

中断返回。

### 描述:

返回的目的地址为中断地址寄存器 ICA 的内容

### 限制条件:

;

操作:

PC ← ICA

异常:

;

备注:

# 4.2.20. INTR

内核: v2

格式:

INTR imm<sub>18</sub>

目的:

软件触发外设中断

描述:

软件指令触发外设中断(设置 INT1~INT14),不受 picmr 位影响

限制条件:

;

操作:

异常:

;

备注:

## 4.2.21. IACK

内核: v3

格式:

IACK imm<sub>18</sub>

目的:

软件触发 CLA task

描述:

软件指令触发 CLA task

限制条件:

;

操作:

异常:

;

备注:

# 4.3. 数据传送指令

### **4.3.1.** MOVIGH

内核: v1

格式:

MOVIGH Rd, imm<sub>16</sub>

目的:

将一个 16 位的立即数复制到 rd 的高 16 位中

描述:

Rd<sub>31..16</sub> **←** imm<sub>16</sub>

限制条件:

Rd 为 GR, OFF, BAR, MR; imm 为 16 位立即数

操作:

GR[Rd]<sub>31..16</sub> ← imm<sub>16</sub>

异常:

;

备注:

### **4.3.2. MOVIGL**

内核: v1

格式:

MOVIGL Rd, imm<sub>16</sub>

目的:

将一个 16 位的立即数复制到 rd 的低 16 位中

描述:

Rd<sub>15..0</sub> **←** imm<sub>16</sub>

限制条件:

Rd 为 GR, OFF, BAR, MR; imm 为 16 位立即数

操作:

GR[Rd]<sub>15..0</sub> ← imm<sub>16</sub>

异常:

;

备注:

### 4.3.3. **MOVG2G**

内核: v1

格式:

MOVG2G Rd, Rs

目的:

将 Rs 中的数移送至 Rd 中

描述:

Rd **←** Rs

限制条件:

Rd 为 GR, OFF, BAR, MR; Rs 为 GR, OFF, BAR, MR

操作:

$GR[Rd] \leftarrow GR[Rs]$

异常:

:

备注:

### 4.3.4. MOVG2C

内核: v1

格式:

MOVG2C Rs

目的:

用 Rs 的内容设置控制寄存器

描述:

Control Register ← Rs

限制条件:

Rs 为 GR

操作:

Control Register ←GR[Rs]

异常:

;

备注:

### 4.3.5. MOVC2G

内核: v1

格式:

MOVC2G Rd

目的:

将控制寄存器的内容保存到 GR 中

描述:

Rs ← Control Register

限制条件:

Rd 为 GR

操作:

GR[Rs] ← Control Register

异常:

:

备注:

### 4.3.6. MOVIGLZ

内核: v2

格式:

MOVIGLZ Rd, imm<sub>16</sub>

目的:

将 rd 的低 16 位写入 16 位立即数,将 rd 的高 16 位写入 0

描述:

Rd<sub>31..0</sub> **←** {16'd0, imm<sub>16</sub>}

限制条件:

Rd 为 GR, OFF, BAR, MR; imm 为 16 位立即数

操作:

GR[Rd]<sub>31..0</sub> ← {16'd0, imm<sub>16</sub>}

异常:

;

备注:

## 4.3.7. MOVIGLX

内核: v2

格式:

MOVIGLX Rd, imm<sub>16</sub>

目的:

将一个 16 位的有符号立即数进行符号位扩展至 32bit 后复制到 rd 中

描述:

$Rd_{31..0} \leftarrow sign\_extend(imm_{16})$

限制条件:

Rd 为 GR, OFF, BAR, MR; imm 为 16 位立即数

操作:

$GR[Rd]_{31..0} \leftarrow sign\_extend(imm_{16})$

异常:

;

备注:

# 4.4. 加载/存储指令

### 4.4.1. LOAD8

内核: v1

格式:

LOAD8 Rd, Rs, imm<sub>9</sub>

目的:

访问存储器,读取目标地址出8bit的数据。

#### 描述:

从内存的目标地址处读取 8bit 的数据,零符号扩展到 32bit,复制到 Rd 中。

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$Rd_{7..0} \leftarrow zero_extend (MEM[Rs + imm_9])$

异常:

;

备注:

### 4.4.2. LOAD16

内核: v1

### 格式:

LOAD16 Rd, Rs, imm<sub>9</sub>

### 目的:

访问存储器,读取目标地址出 16bit 的数据。

### 描述:

从内存的目标地址处读取 16bit 的数据,零符号扩展到 32bit,复制到 Rd 中。地址偏移量为 imm<sub>9</sub> 左移一位。

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$Rd_{15..0} \leftarrow MEM[Rs + imm_9 << 1]$

### 异常:

访存地址最低位不为0,则发出异常;

### 备注:

### 4.4.3. LOAD32

内核: v1

### 格式:

LOAD32 Rd, Rs, imm<sub>9</sub>

### 目的:

访问存储器,读取目标地址出 32bit 的数据。

### 描述:

从内存的目标地址处读取 32bit 的数据,存放在 Rd 中。地址偏移量为 imm9 左移 2 位。

### 限制条件:

Rd为GR,Rs为GR,imm为9位立即数

### 操作:

Rd  $\leftarrow$  MEM[Rs + imm<sub>9</sub> << 2]

### 异常:

访存地址最低两位不为00,则发出异常;

#### 备注:

### 4.4.4. STORE8

内核: v1

格式:

STORE8 Rd, Rs, imm<sub>9</sub>

目的:

写存储器,将 8bit 数据写入内存的目标地址处。

描述:

将 Rd 的低 8bit 数据写入内存的目标地址处。

限制条件:

Rd为GR, Rs为GR, imm为9位立即数

操作:

$MEM[Rs + imm_9] \leftarrow Rd_{7..0}$

异常:

;

备注:

### 4.4.5. STORE16

内核: v1

### 格式:

STORE16 Rd, Rs, imm<sub>9</sub>

### 目的:

写存储器,将 16bit 数据写入内存的目标地址处。

### 描述:

将 Rd 的低 16bit 数据写入内存的目标地址处。地址偏移量为 immg 左移 1 位。

### 限制条件:

Rd为GR,Rs为GR,imm为9位立即数

### 操作:

### 异常:

访存地址最低位不为0,则发出异常;

#### 备注:

### 4.4.6. STORE32

内核: v1

### 格式:

STORE32 Rd, Rs, imm<sub>9</sub>

### 目的:

写存储器,将 32bit 数据写入内存的目标地址处。地址偏移量为 imm9 左移 2 位。

### 描述:

将 Rd 中数据写入内存的目标地址处。

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$MEM[Rs + imm_9 << 2] \leftarrow Rd$

### 异常:

访存地址最低两位不为00,则发出异常。

#### 备注:

### 4.4.7. LOADU8

内核: v1

### 格式:

LOADU8 Rd, Rs, imm<sub>9</sub>

### 目的:

访问存储器,读取目标地址出8bit的数据。并且更新基址寄存器。

### 描述:

从内存的目标地址处读取 8bit 的数据,存放在 Rd 的低位。同时更新基址寄存器 Rs

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$Rd_{7..0} \leftarrow MEM[Rs + imm_9]$

Rs ← Rs + imm<sub>9</sub>

异常:

;

备注:

### 4.4.8. **LOADU16**

内核: v1

### 格式:

LOADU16 Rd, Rs, imm<sub>9</sub>

### 目的:

访问存储器,读取目标地址出 16bit 的数据。并且更新基址寄存器。

### 描述:

从内存的目标地址处读取 16bit 的数据,存放在 Rd 的低位,同时更新基址寄存器 Rs。地址偏移量为 immg 左移 1 位

#### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$Rd_{15..0} \leftarrow MEM[Rs + imm_9 << 1]$

Rs **←** Rs + imm<sub>9</sub> << 1

#### 异常:

访存地址最低位不为0,则发出异常;

### 备注:

### 4.4.9. LOADU32

内核: v1

### 格式:

LOADU32 Rd, Rs, imm<sub>9</sub>

### 目的:

访问存储器,读取目标地址出32bit的数据。并且更新基址寄存器。

### 描述:

从内存的目标地址处读取 32bit 的数据,存放在 Rd 中,同时更新基址寄存器 Rs. 地址偏移量为 imm<sub>9</sub> 左移 2 位

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

Rd  $\leftarrow$  MEM[Rs + imm<sub>9</sub> << 2]

Rs  $\leftarrow$  Rs + imm<sub>9</sub> << 2

#### 异常:

访存地址最低两位不为00,则发出异常;

### 备注:

### 4.4.10. STOREU8

内核: v1

格式:

STOREU8 Rd, Rs, imm<sub>9</sub>

目的:

写存储器,将 8bit 数据写入内存的目标地址处。同时更新基址寄存器。

描述:

将 Rd 的低 8bit 数据写入内存的目标地址处,同时更新基址寄存器 Rs。

限制条件:

Rd为GR, Rs为GR, imm为9位立即数

操作:

$MEM[Rs + imm_9] \leftarrow Rd_{7..0}$

Rs ← Rs +imm<sub>9</sub>

异常:

;

备注:

### 4.4.11. STOREU16

内核: v1

### 格式:

STOREU16 Rd, Rs, imm<sub>9</sub>

### 目的:

写存储器,将 16bit 数据写入内存的目标地址处。同时更新基址寄存器。

### 描述:

将 Rd 的低 16bit 数据写入内存的目标地址处,同时更新基址寄存器 Rs。地址偏移量为 imm9 左移 1 位

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

Rs **←** Rs +imm<sub>9</sub> << 1

#### 异常:

访存地址最低位不为 0,则发出异常;

### 备注:

### 4.4.12. STOREU32

内核: v1

### 格式:

STOREU32 Rd, Rs, imm<sub>9</sub>

### 目的:

写存储器,将 32bit 数据写入内存的目标地址处。同时更新基址寄存器。

### 描述:

将 Rd 的数据写入内存的目标地址处,同时更新基址寄存器 Rs。地址偏移量为 immg 左移 2 位

### 限制条件:

Rd为GR, Rs为GR, imm为9位立即数

### 操作:

$\mathsf{MEM}[\mathsf{Rs} + \mathsf{imm}_9 << 2] \; \longleftarrow \; \mathsf{Rd}$

Rs **←** Rs +imm<sub>9</sub> << 2

#### 异常:

访存地址最低两位不为00,则发出异常;

### 备注:

#### 4.4.13. LOADO16

内核: v1

#### 格式:

LOADO16 Rd, Rs, Rt

#### 目的:

循环访问存储器,读取目标地址出 16bit 的数据。

#### 描述:

从内存的目标地址处读取 16bit 的数据,存放在 Rd 的低位。Rt 对应一组寄存器:BAR, OFF, MR。取完后需要递增 Rs,递增的步长为 OFF,但是需要保证 Rs 不超过 BAR+MR,如果超过则将模 MR。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 BAR、OFF、MR。

#### 操作:

```

Rd<sub>15..0</sub> ← MEM[Rs]

IF Rs + OFF > MR + BAR

Rs = Rs + OFF − MR

ELSE IF Rs + OFF < BAR

Rs = Rs + OFF + MR

ELSE

```

LJE

Rs = Rs + OFF

#### 异常:

访存地址最低位不为0,则发出异常;

### 备注:

#### 4.4.14. LOADO32

内核: v1

#### 格式:

LOADO32 Rd, Rs, Rt

#### 目的:

循环访问存储器,读取目标地址出 32bit 的数据。

#### 描述:

从内存的目标地址处读取 32bit 的数据,存放在 Rd 中。Rt 对应一组寄存器:BAR, OFF, MR。取完后需要递增 Rs,递增的步长为 OFF,但是需要保证 Rs 不超过 BAR + MR,如果超过则将模 MR。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 BAR、OFF、MR。

#### 操作:

Rd ← MEM[Rs]

IF Rs + OFF > MR + BARRs = Rs + OFF - MR

ELSE IF Rs + OFF < BAR

Rs = Rs + OFF + MR

**ELSE**

Rs = Rs + OFF

### 异常:

访存地址最低两位不为00,则发出异常;

#### 备注:

使用实例: loado32 gr0 gr1 bar1

其中, bar - base address, off – offset ,mr – modulus

三个 MOR 寄存器共有 4 组, 见寄存器简述部分;

#### 4.4.15. STOREO16

内核: v1

#### 格式:

STOREO16 Rd, Rs, Rt

#### 目的:

循环写存储器,向目标地址写 16bit 的数据。

#### 描述:

将 Rd 的低 16 位写入内存的目标地址处。Rt 对应一组寄存器:BAR, OFF, MR。写完后需要递 增 Rs, 递增的步长为 OFF, 但是需要保证 Rs 不超过 BAR + MR, 如果超过则将模 MR 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 BAR、OFF、MR。

### 操作:

$MEM[Rs] \leftarrow Rd_{15..0}$ IF Rs + OFF > MR + BAR Rs = Rs + OFF - MR**ELSE IF** Rs + OFF < BAR Rs = Rs + OFF + MR**ELSE**

Rs = Rs + OFF

#### 异常:

访存地址最低位不为0,则发出异常;

#### 备注:

### 4.4.16. STOREO32

内核: v1

#### 格式:

STOREO32 Rd, Rs, Rt

#### 目的:

循环写存储器,向目标地址写 32bit 的数据。

#### 描述:

将 Rd 的数据写入内存的目标地址处。Rt 对应一组寄存器:BAR, OFF, MR。写完后需要递增 Rs,递增的步长为 OFF,但是需要保证 Rs 不超过 BAR + MR,如果超过则将模 MR

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 BAR、OFF、MR。

### 操作:

MEM[Rs] ← Rd

IF Rs + OFF > MR + BAR

Rs = Rs + OFF - MR

**ELSE IF** Rs + OFF < BAR

Rs = Rs + OFF + MR

**ELSE**

Rs = Rs + OFF

#### 异常:

访存地址最低两位不为00,则发出异常;

#### 备注:

### 4.4.17. LOADI8

内核: v2

### 格式:

LOADI8 Rd, imm<sub>15</sub>

### 目的:

访问存储器,读取目标地址出8bit的数据。

### 描述:

从内存的目标地址处读取 8bit 的数据,零符号扩展到 32bit,复制到 Rd 中。

### 限制条件:

Rd 为 GR, imm 为 15 位立即数

### 操作:

$Rd_{7..0} \leftarrow zero\_extend (MEM[imm_{15}])$

异常:

;

备注:

### 4.4.18. LOADI16

内核: v2

### 格式:

LOADI16 Rd, imm<sub>15</sub>

### 目的:

访问存储器,读取目标地址出 16bit 的数据。

### 描述:

从内存的目标地址处读取 16bit 的数据,零符号扩展到 32bit,复制到 Rd 中。地址偏移量为  $imm_{15}$  左移一位。

### 限制条件:

Rd 为 GR, imm 为 15 位立即数

### 操作:

Rd<sub>15..0</sub> ← MEM[ imm<sub>15</sub> << 1]

### 异常:

访存地址最低位不为0,则发出异常;

### 备注:

### 4.4.19. LOADI32

内核: v2

### 格式:

LOADI32 Rd, imm<sub>15</sub>

### 目的:

访问存储器,读取目标地址出 32bit 的数据。

### 描述:

从内存的目标地址处读取 32bit 的数据,存放在 Rd 中。地址偏移量为 imm<sub>15</sub> 左移 2 位。

### 限制条件:

Rd 为 GR, imm 为 15 位立即数

### 操作:

Rd **←** MEM[imm<sub>15</sub> << 2]

### 异常:

访存地址最低两位不为00,则发出异常;

#### 备注:

### 4.4.20. STOREI8

内核: v2

格式:

STOREI8 Rd, imm<sub>15</sub>

目的:

写存储器,将 8bit 数据写入内存的目标地址处。

描述:

将 Rd 的低 8bit 数据写入内存的目标地址处。

限制条件:

Rd 为 GR, imm 为 15 位立即数

操作:

MEM[imm<sub>15</sub>] **←** Rd<sub>7..0</sub>

异常:

;

备注:

### 4.4.21. STOREI16

内核: v2

### 格式:

STOREI16 Rd, imm<sub>15</sub>

### 目的:

写存储器,将 16bit 数据写入内存的目标地址处。

### 描述:

将 Rd 的低 16bit 数据写入内存的目标地址处。地址偏移量为 imm<sub>15</sub> 左移 1 位。

### 限制条件:

Rd 为 GR, imm 为 15 位立即数

### 操作:

MEM[imm<sub>15</sub> << 1] ← Rd<sub>15..0</sub>

### 异常:

访存地址最低位不为0,则发出异常;

#### 备注:

### 4.4.22. STOREI32

内核: v2

### 格式:

STOREI32 Rd, imm<sub>15</sub>

### 目的:

写存储器,将 32bit 数据写入内存的目标地址处。地址偏移量为 imm<sub>15</sub> 左移 2 位。

### 描述:

将 Rd 中数据写入内存的目标地址处。

### 限制条件:

Rd 为 GR, imm 为 15 位立即数

### 操作:

MEM[imm<sub>15</sub> << 2] **←** Rd

### 异常:

访存地址最低两位不为00,则发出异常。

#### 备注:

# 4.5. 标量运算指令 - 比较指令

标量运算操作数 Rd, Rs, Rt 都是 GR, 标量指令都是整数运算

## 4.5.1. EQI

```

内核: v1

```

格式:

EQI Rs, imm<sub>9</sub>

目的:

有符号判断。比较两个32位数是否相等

### 描述:

```

immg有符号扩展至 32bit 进行比较

```

```

CON = (Rs == sign extend (imm<sub>9</sub>))

```

### 限制条件:

Rs为GR,imm为9位立即数

### 操作:

```

IF GR[Rs] == sign_extend(imm<sub>9</sub>)

```

CON = 1;

**ELSE**

CON = 0;

异常:

•

备注:

# 4.5.2. **NEQI**

```

内核: v1

格式:

NEQI Rs, imm<sub>9</sub>

目的:

有符号判断。比较两个32位数是否相等

描述:

imm9有符号扩展至 32bit 进行比较

CON = (Rs != sign_extend (imm<sub>9</sub>))

限制条件:

Rs 为 GR, imm 为 9 位立即数

操作:

IF GR[Rs] != sign_extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.3. GTI

```

内核: v1

格式:

GTI Rs, imm<sub>9</sub>

目的:

有符号判断。比较 Rs 是否大于立即数 imm

描述:

imm9有符号扩展至 32bit 进行比较

CON = (Rs > sign_extend (imm<sub>9</sub>))

限制条件:

Rs 为 GR, imm 为 9 位立即数

操作:

IF GR[Rs] > sign_extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.4. LTI

```

内核: v1

格式:

LTI Rs, imm<sub>9</sub>

目的:

有符号判断。比较 Rs 是否小于立即数 imm

描述:

imm9有符号扩展至 32bit 进行比较

CON = (Rs < sign_extend (imm<sub>9</sub>))

限制条件:

Rs 为 GR, imm 为 9 位立即数

操作:

IF GR[Rs] < sign_extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.5. **GEI**

```

内核: v1

格式:

GEI Rs, imm<sub>9</sub>

目的:

有符号判断。比较 Rs 是否大于等于立即数 imm

描述:

imm9有符号扩展至 32bit 进行比较

CON = (Rs >= sign_extend (imm<sub>9</sub>))

限制条件:

Rs 为 GR, imm 为 9 位立即数

操作:

IF GR[Rs] >= sign_extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.6. LEI

内核: v1 格式:

LEI Rs, imm<sub>9</sub>

目的:

有符号判断。Rs 是否小于等于立即数 imm

# 描述:

imm9有符号扩展至 32bit 进行比较

CON = (Rs <= sign\_extend (imm<sub>9</sub>))

# 限制条件:

Rs 为 GR, imm 为 9 位立即数

# 操作:

IF GR[Rs] <= sign\_extend(imm<sub>9</sub>)

CON = 1;

**ELSE**

CON = 0;

异常:

:

备注:

# 4.5.7. EQ

内核: v1

格式:

EQ Rs, Rt

目的:

有符号判断。比较两个32位数是否相等

描述:

CON = (Rs == Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] == GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

;

备注:

# 4.5.8. NEQ

内核: v1

格式:

NEQ Rs, Rt

目的:

有符号判断。比较两个32位数是否不相等

描述:

CON = (Rs != Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] != GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

;

备注:

# 4.5.9. GT

内核: v1

格式:

GT Rs, Rt

目的:

有符号判断。比较 Rs 是否大于 Rt。

描述:

CON = (Rs > Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] > GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.10. LT

内核: v1

格式:

LT Rs, Rt

目的:

有符号判断。比较 Rs 是否小于 Rt。

描述:

CON = (Rs < Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] < GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.11. GE

内核: v1

格式:

GE Rs, Rt

目的:

有符号判断。比较 Rs 是否大于等于 Rt。

描述:

CON = (Rs >= Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] >= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

;

备注:

# 4.5.12. LE

内核: v1

格式:

LE Rs, Rt

目的:

有符号判断。比较 Rs 是否小于等于 Rt

描述:

CON = (Rs <= Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] <= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.13. GTU

内核: v1

格式:

GTU Rs, Rt

目的:

无符号判断。比较 Rs 是否大于 Rt。

描述:

CON = (Rs > Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] > GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.14. LTU

内核: v1

格式:

LTU Rs, Rt

目的:

无符号判断。比较 Rs 是否小于 Rt。

描述:

CON = (Rs < Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] < GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.15. **GEU**

内核: v1

格式:

GEU Rs, Rt

目的:

无符号判断。比较 Rs 是否大于等于 Rt。

描述:

CON = (Rs >= Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] >= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.16. LEU

内核: v1

格式:

LEU Rs, Rt

目的:

无符号判断。比较 Rs 是否小于等于 Rt

描述:

CON = (Rs <= Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] <= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# 4.5.17. TEST

内核: v1

格式:

TEST Rs, Rt

目的:

测试 Rs 中某一位是否为 1

# 描述:

测试 Rs 的第 Rt 位是否为 1 (最低位定义为第 0 位)

# 限制条件:

Rs为GR,Rt为GR

# 操作:

**IF** GR[Rs]<sub>Rt</sub> == 1 CON = 1;

**ELSE**

CON = 0;

异常:

;

备注:

,

# 4.5.18. TESTI

内核: v1

#### 格式:

TESTI Rs, imm<sub>5</sub>

# 目的:

测试 Rs 中某一位是否为 1

# 描述:

测试 Rs 的第 imm5 位是否为 1 (最低位定义为第 0 位)

# 限制条件:

Rs 为 GR, imm 为 5 位立即数

# 操作:

**IF** GR[Rs]<sub>imm</sub> == 1 CON = 1;

**ELSE**

CON = 0;

# 异常:

;

### 备注:

# 4.5.19. EQU

内核: v2

格式:

EQU Rs, Rt

目的:

无符号判断。比较两个32位数是否相等

描述:

CON = (Rs == Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] == GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

;

备注:

# **4.5.20. NEQU**

内核: v2

格式:

NEQU Rs, Rt

目的:

无符号判断。比较两个32位数是否不相等

描述:

CON = (Rs != Rt)

限制条件:

Rs 为 GR,Rt 为 GR

操作:

IF GR[Rs] != GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

.

备注:

# **4.5.21. EQIU**

```

内核: v2

格式:

EQIU Rs, imm<sub>9</sub>

目的:

无符号判断。比较两个32位数是否相等

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs == extend (imm<sub>9</sub>))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] == extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.22. **NEQIU**

```

内核: v2

格式:

NEQIU Rs, imm<sub>9</sub>

目的:

无符号判断。比较两个32位数是否相等

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs != extend (imm<sub>9</sub>))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] != extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.23. GTIU

```

内核: v2

格式:

GTIU Rs, imm<sub>9</sub>

目的:

无符号判断。比较 Rs 是否大于立即数 imm

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs > extend (imm_9))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] > extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.24. LTIU

```

内核: v2

格式:

LTIU Rs, imm<sub>9</sub>

目的:

无符号判断。比较 Rs 是否小于立即数 imm

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs < extend (imm<sub>9</sub>))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] < extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.25. **GEIU**

```

内核: v2

格式:

GEIU Rs, imm<sub>9</sub>

目的:

无符号判断。比较 Rs 是否大于等于立即数 imm

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs >= extend (imm<sub>9</sub>))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] >= extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.5.26. LEIU

```

内核: v2

格式:

LEIU Rs, imm<sub>9</sub>

目的:

无符号判断。Rs 是否小于等于立即数 imm

描述:

extend (imm<sub>9</sub>) = \{21'd0, imm_9\}

CON = (Rs <= extend (imm<sub>9</sub>))

限制条件:

Rs为GR,imm为9位立即数

操作:

IF GR[Rs] <= extend(imm<sub>9</sub>)

CON = 1;

ELSE

CON = 0;

异常:

备注:

```

# 4.6. 标量运算指令 - 运算指令

#### **4.6.1. ADDI**

内核: v1

格式:

ADDI Rd, Rs, imm<sub>11</sub>

目的:

将一个 32 位数与一个常数相加得到结果

#### 描述:

Rd ← Rs + imm<sub>11</sub>

Imm 进行符号扩展至 32 位(加法运算只是局限在低 11 位,即加到 0x7ff 时即会拓展到 0xfffffffff 时再加高于 11 位有效的值时不变,但是加 1 之后就会变为 0,即运算只是局限在低 11 位)。最高位产生进位则置 CARRY 位。

#### 限制条件:

Rd 为 GR, Rs 为 GR, imm 为 11 位立即数

#### 操作:

{CARRY,, GR[Rd]}  $\leftarrow$   $GR[Rs] + sign extend (imm_{11})$

#### 异常:

根据结果是否溢出设置 OF;

#### 备注:

# **4.6.2. ADDIC**

内核: v1

#### 格式:

ADDIC Rd, Rs, imm<sub>11</sub>

#### 目的:

将一个32位数和一个常数相加,低位再加上CARRY位得到结果。

#### 描述:

Rd ← Rs + imm + CARRY

Imm 进行符号扩展至 32 位。最高位产生进位则置 CARRY 位。

### 限制条件:

Rd 为 GR, Rs 为 GR, imm 为 11 位立即数

# 操作:

{CARRY, GR[Rd]}  $\leftarrow$   $GR[Rs] + sign\_extend (imm_{11}) + CARRY$

#### 异常:

根据结果是否溢出设置 OF:

#### 备注:

# 4.6.3. ADD

内核: v1

格式:

ADD Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数相加得到结果

描述:

Rd ← Rs + Rt

最高位产生进位则置 CARRY 位。

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

{CARRY, GR[Rd]}  $\leftarrow$  GR[Rs] + GR[Rt]

异常:

根据结果是否溢出设置 OF:

备注:

# 4.6.4. ADDC

内核: v1

格式:

ADDC Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数相加,低位加上 CARRY 位得到结果

描述:

Rd ← Rs + Rt + CARRY

最高位产生进位则置 CARRY 位。

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

$\{CARRY, GR[Rd]\} \leftarrow GR[Rs] + GR[Rt] + CARRY$

异常:

根据结果是否溢出设置 OF:

备注:

# 4.6.5. SUB

内核: v1

格式:

SUB Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数相减得到结果

描述:

$Rd \leftarrow Rs - Rt$

最高位产生借位则置 CARRY 位。

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

{CARRY, GR[Rd]}  $\leftarrow$  GR[Rs] - GR[Rt]

异常:

根据结果是否溢出设置 OF:

备注:

#### 4.6.6. SUBC

内核: v1

格式:

SUBC Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数相减,低位减去 CARRY 得到结果

#### 描述:

Rd ← Rs – Rt – CARRY

最高位产生借位则置 CARRY 位。

### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

# 操作:

$\{CARRY, GR[Rd]\} \leftarrow GR[Rs] - GR[Rt] - CARRY$

# 异常:

根据结果是否溢出设置 OF:

#### 备注:

.

### 4.6.7. MUL32

内核: v1

#### 格式:

MUL32 Rd, Rs, Rt

### 目的:

将一个 32 位整数与一个 32 位整数进行有符号相乘得到结果的低 32 位。

#### 描述:

将 Rs 和 Rt 中的 32 位数据有符号相乘得到 64 位数据,截取低 32 位存在 Rd 中。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

### 操作:

temp ← GR[Rs] \* GR[Rt]

$GR[Rd] \leftarrow temp_{31..0}$

异常:

;

备注:

# 4.6.8. MUL64

内核: v1

格式:

MUL64 Rd, Rs, Rt

目的:

将一个 32 位整数与一个 32 位整数有符号相乘得到结果的高 32 位。

#### 描述:

将 Rs 和 Rt 中的 32 位数据有符号相乘得到 64 位数据,截取高 32 位存在 Rd 中。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

### 操作:

temp ← GR[Rs] \* GR[Rt]

$GR[Rd] \leftarrow temp_{63..32}$

异常:

;

备注:

### 4.6.9. MULU32

内核: v1

#### 格式:

MULU32 Rd, Rs, Rt

### 目的:

将一个 32 位整数与一个 32 位整数无符号相乘得到结果的低 32 位。

#### 描述:

将 Rs 和 Rt 中的 32 位数据无符号相乘得到 64 位数据,将其低 32 位保存在 Rd 中。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

### 操作:

temp ← GR[Rs] \* GR[Rt]

$GR[Rd] \leftarrow temp_{31..0}$

异常:

;

备注:

# 4.6.10. MAX

```

内核: v1

格式:

MAX Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数按照有符号数进行比较,得到较大的那个数

描述:

Rd ← Rs > Rt? Rs: Rt

限制条件:

Rd为GR, Rs为GR, Rt为GR

操作:

IF GR[Rs] > GR[Rt]

GR[Rd] ← GR[Rs]

ELSE

GR[Rd] \leftarrow GR[Rt]

异常:

备注:

```

# 4.6.11. MIN

```

内核: v1

格式:

MIN Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数按照有符号数进行比较,得到较小的那个数

描述:

Rd ← Rs < Rt? Rs: Rt

限制条件:

Rd为GR, Rs为GR, Rt为GR

操作:

IF GR[Rs] < GR[Rt]</pre>

GR[Rd] \leftarrow GR[Rs]

ELSE

GR[Rd] \leftarrow GR[Rt]

异常:

备注:

```

## 4.6.12. ABS

内核: v1

格式:

ABS Rd, Rs

目的:

得到一个 32 位有符号数的绝对值

描述:

Rd **←** |Rs|

限制条件:

Rd为GR,Rs为GR

操作:

$GR[Rd] \leftarrow |GR[Rs]|$

异常:

根据结果是否溢出设置 OF;

备注:

:

## 4.6.13. CBW

内核: v1

格式:

CBW Rd, Rs

目的:

整数有符号扩展。

描述:

将 Rs 的低 8 位进行有符号扩展至 32 位后保存在 Rd 中

限制条件:

Rd 为 GR,Rs 为 GR

操作:

$GR[Rd] \leftarrow sign\_extend (GR[Rs]_{7..0})$

异常:

;

备注:

## 4.6.14. CHW

内核: v1

格式:

CHW Rd, Rs

目的:

整数有符号扩展。

描述:

将 Rs 的低 16 位进行有符号扩展至 32 位后保存在 Rd 中

限制条件:

Rd 为 GR,Rs 为 GR

操作:

GR[Rd] ← sign\_extended (GR[Rs]<sub>15..0</sub>)

异常:

:

备注:

#### 4.6.15. SAT64

内核: v1

#### 格式:

SAT64 Rd, Rs

#### 目的:

根据溢出结果对 64 位内容做饱和。

#### 描述:

Rs+1 和 Rs 两个 32 位寄存器组合成 64 位源操作数,其中 Rs+1 存放 64 位数高 32 位,Rs 存放 64 位数低 32 位,比较溢出计数器 OVC 的值与 0,结果写入 Rd 表示写入 Rd+1 和 Rd 两个 32 位寄存器组合,作为目的寄存器,其中 Rd+1 存放 64 位结果高 32 位,Rd 存放 64 位结果低 32 位。

#### 限制条件:

Rd 为 GR, Rs 为 GR, 且 Rd、Rs 必须为偶数

#### 操作:

{GR[Rd+1], GR[Rd]} = {GR[Rs+1], GR[Rs]};

#### 异常:

IF OVC = 0

备注:

#### 4.6.16. NEG

内核: v2

格式:

**NEG Rd**

目的:

32 位有符号整数取负

#### 描述:

对 GR[Rs]中存放的 32 位有符号整数取负 (取反后+1), 结果存到 GR[Rd]。

#### 限制条件:

Rd 为 GR

#### 操作:

if (Rs == 0x80000000) Rd = 0x80000000; else

Rd = -Rs;

异常:

;

#### 备注:

若操作数为 0x80000000 (-2147483648),则设置溢出标志位为 1,否则置 0。

## 4.6.17. SUBI

内核: v2

#### 格式:

SUBI Rd, Rs,  $imm_{11}$

#### 目的:

将一个 32 位数与一个 32 位数相减得到结果

#### 描述:

Rd ← Rs − imm<sub>11</sub>

Imm 进行符号扩展至 32 位,最高位产生借位则置 CARRY 位。

## 限制条件:

Rd 为 GR, Rs 为 GR, imm<sub>11</sub> 为 11 为立即数

## 操作:

{CARRY, GR[Rd]} ← GR[Rs] −sign\_extend (imm<sub>11</sub>)

## 异常:

根据结果是否溢出设置 OF:

#### 备注:

#### 4.6.18. SUBIC

内核: v2

#### 格式:

SUBIC Rd, Rs, imm<sub>11</sub>

#### 目的:

将一个 32 位数与一个 32 位数相减,低位减去 CARRY 得到结果

#### 描述:

Rd ← Rs − imm<sub>11</sub> − CARRY

Imm 进行符号扩展至 32 位。最高位产生进位则置 CARRY 位。

## 限制条件:

Rd 为 GR, Rs 为 GR, imm<sub>11</sub> 为 11 为立即数

## 操作:

{CARRY, GR[Rd]}  $\leftarrow$   $GR[Rs] - sign\_extend (imm_{11}) - CARRY$

#### 异常:

根据结果是否溢出设置 OF:

#### 备注:

备注:

## **4.6.19. SELECT**

```

内核: v2

格式:

SELECT Rd, Rs, Rt

目的:

根据 CR 中的条件标志位,选择 GR 的数值来源

描述:

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

if CON

{

Rd <= Rs

}

else

{

Rd <= Rt

}

异常:

```

## 4.6.20. SETC

备注:

```

内核: v2

格式:

SETC Rd

目的:

根据 CR 中的条件标志位,选择 GR 的数值来源

描述:

限制条件:

Rd 为 GR

操作:

if CON

{

Rd <= 1

}

else

{

Rd \le 0

}

异常:

```

## 4.6.21. MULU64

内核: v2

#### 格式:

MULU.32 Rd, Rs, Rt

#### 目的:

将一个 32 位整数与一个 32 位整数无符号相乘得到结果的高 32 位。

#### 描述:

将 Rs 和 Rt 中的 32 位数据无符号相乘得到 64 位数据,将其高 32 位保存在 Rd 中。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

## 操作:

temp ← GR[Rs] \* GR[Rt]

$GR[Rd] \leftarrow temp_{63..32}$

异常:

备注:

## 4.6.22. MAC16

内核: v2

#### 格式:

MAC16 Rd, Rs, Rt

#### 目的:

有符号双 16 位定点整数乘累加指令

#### 描述:

有符号双 16 位定点整数乘累加指令,对 Rs 和 Rd 的高 16 位和低 16 位分开进行 16 位乘法,即 Rs\_h\*Rt\_h+Rd\_h和 Rs\_l\*Rt\_l+Rd\_l。得到的 64 位结果,高 32 位结果为 Rs\_h\*Rt\_h+Rd\_h,存放到 Rd+1;低 32 位结果为 Rs\_l\*Rt\_l+Rd\_l,存放到 Rd。

## 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

#### 操作:

GR[Rd] **←**Rs\_I \* Rt\_I + Rd\_I

$GR[Rd+1] \leftarrow Rs_h * Rt_h + Rd_h$

#### 异常:

;

#### 备注:

## 4.6.23. MACU16

内核: v2

#### 格式:

MACU16 Rd, Rs, Rt

#### 目的:

无符号双 16 位定点整数乘累加指令

#### 描述:

无符号双 16 位定点整数乘累加指令,对 Rs 和 Rd 的高 16 位和低 16 位分开进行 16 位乘法,即 Rs\_h \* Rt\_h + Rd\_h 和 Rs\_l \* Rt\_l + Rd\_l。得到的 64 位结果,高 32 位结果为 Rs\_h \* Rt\_h + Rd\_h,存放到 Rd+1;低 32 位结果为 Rs\_l \* Rt\_l + Rd\_l,存放到 Rd。

## 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

#### 操作:

$$GR[Rd] \leftarrow Rs_I * Rt_I + Rd_I$$

$GR[Rd+1] \leftarrow Rs_h * Rt_h + Rd_h$

异常:

#### 备注:

#### 4.6.24. MAC32

内核: v2

#### 格式:

MAC32 Rd, Rs, Rt

#### 目的:

将一个 32 位整数与一个 32 位整数进行有符号相乘后加上一个 32 位累加数得到结果的低 32 位。

#### 描述:

32 位有符号数乘累加指令,取低 32 位结果。将 Rs 和 Rt 中的 32 位数据有符号相乘后再加上 Rd 中的 32 位数据得到 64 位数据,截取低 32 位存在 Rd 中。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

temp  $\leftarrow$  GR[Rs] \* GR[Rt] + GR[Rd] GR[Rd]  $\leftarrow$  temp<sub>31..0</sub>

#### 异常:

#### 备注:

## 4.6.25. MAC64

内核: v2

#### 格式:

MAC64 Rd, Rs, Rt

#### 目的:

将一个 32 位整数与一个 32 位整数进行有符号相乘后加上一个 32 位累加数得到结果的高 32 位。

#### 描述:

32 位有符号数乘累加指令,取高 32 位结果。将 Rs 和 Rt 中的 32 位数据有符号相乘后再加上 Rd 中的 32 位数据得到 64 位数据,截取高 32 位存在 Rd 中。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

temp  $\leftarrow$  GR[Rs] \* GR[Rt] + GR[Rd] GR[Rd]  $\leftarrow$  temp<sub>63..32</sub>

#### 异常:

备注:

## 4.6.26. MACU32

内核: v2

#### 格式:

MACU32 Rd, Rs, Rt

#### 目的:

将一个 32 位整数与一个 32 位整数进行无符号相乘后加上一个 32 位累加数得到结果的高 =低 32 位。

#### 描述:

32 位无符号数乘累加指令,取低 32 位结果。将 Rs 和 Rt 中的 32 位数据无符号相乘后再加上 Rd 中的 32 位数据得到 64 位数据,截取低 32 位存在 Rd 中。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

temp ← GR[Rs] \* GR[Rt] + GR[Rd]

$GR[Rd] \leftarrow temp_{31..0}$

#### 异常:

:

#### 备注:

#### 4.6.27. MACU64

内核: v2

#### 格式:

MACU.64 Rd, Rs, Rt

#### 目的:

将一个 32 位整数与一个 32 位整数进行无符号相乘后加上一个 32 位累加数得到结果的高 32 位。

#### 描述:

32 位无符号数乘累加指令,取高 32 位结果。将 Rs 和 Rt 中的 32 位数据无符号相乘后再加上 Rd 中的 32 位数据得到 64 位数据,截取高 32 位存在 Rd 中。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

```

temp ← GR[Rs] * GR[Rt] + GR[Rd]

```

GR[Rd] **←** temp<sub>63..32</sub>

#### 异常:

;

#### 备注:

# 4.7. 标量运算指令 - 逻辑指令

## 4.7.1. AND

内核: v1

格式:

AND Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数按位与得到结果

描述:

Rd **←** Rs & Rt

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

$GR[Rd] \leftarrow GR[Rs] \& GR[Rt]$

异常:

;

备注:

## 4.7.2. OR

内核: v1

格式:

OR Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数按位或得到结果

描述:

Rd **←** Rs | Rt

限制条件:

Rd为GR, Rs为GR, Rt为GR

操作:

GR[Rd] ← GR[Rs] | GR[Rt]

异常:

;

备注:

## 4.7.3. **XOR**

内核: v1

格式:

XOR Rd, Rs, Rt

目的:

将一个 32 位数与一个 32 位数按位异或得到结果

描述:

Rd ← Rs ^ Rt

限制条件:

Rd为GR, Rs为GR, Rt为GR

操作:

GR[Rd] ← GR[Rs] ^ GR[Rt]

异常:

;

备注:

## 4.7.4. NOT

内核: v1

格式:

NOT Rd, Rs

目的:

将一个 32 位数按位取反得到结果

描述:

Rd **←** ~Rs

限制条件:

Rd 为 GR,Rs 为 GR

操作:

$GR[Rd] \leftarrow GR[Rs]$

异常:

:

备注:

## 4.7.5. SL

内核: v1

#### 格式:

SL Rd, Rs, Rt

#### 目的:

将一个 32 位数进行左移(空出的低位补零)得到结果,保存低 32 位

#### 描述:

Rd ← Rs << Rt

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

## 操作:

temp ← GR[Rs] << GR[Rt]

$GR[Rd] \leftarrow temp_{31..0}$

## 异常:

根据结果是否溢出设置 OF:

#### 备注:

.

## 4.7.6. SRA

内核: v1

格式:

SRA Rd, Rs, Rt

目的:

将一个 32 位数进行算数右移得到结果

描述:

Rd ← Rs >>> Rt

空出的高位补符号位

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

$GR[Rd] \leftarrow GR[Rs] >>> GR[Rt]$

异常:

根据结果是否溢出设置 OF:

备注:

## 4.7.7. SRL

内核: v1

格式:

SRL Rd, Rs, Rt

目的:

将一个 32 位数进行逻辑右移得到结果

描述:

Rd ← Rs >> Rt

空出的高位补零

限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

$GR[Rd] \leftarrow GR[Rs] >> GR[Rt]$

异常:

根据结果是否溢出设置 OF;

备注:

#### 4.7.8. **NEG64**

内核: v1

格式:

NEG64 Rd, Rs

目的:

将一个64位数按位取反。

#### 描述:

(Rd+1), Rd ← ~(Rs+1), ~Rs

Rs+1 和 Rs 两个 32 位寄存器组合成 64 位源操作数,其中 Rs+1 存放 64 位数高 32 位,Rs 存放 64 位数低 32 位,将源操作数按位取反,结果写入 Rd 表示写入 Rd+1 和 Rd 两个 32 位寄存器组合,作为目的寄存器,其中 Rd+1 存放 64 位结果高 32 位,Rd 存放 64 位结果低 32 位。

#### 限制条件:

Rd为GR, Rs为GR, 且Rd、Rs必须为偶数

#### 操作:

$\{GR[Rd+1], GR[Rd]\} = {}^{GR[Rs+1], GR[Rs]\};$

异常:

ĺ

#### 备注:

该指令实际上应该命名为 NOT64;

#### 4.7.9. SRA64

内核: v1

#### 格式:

SRA64 Rd, Rs, Rt

#### 目的:

将 64 位源操作数进行算数右移指定位。

#### 描述:

将 Rs+1, Rs 中的 64 位源操作数进行算数右移 Rt 寄存器低 6 位指定的量,其中 Rs+1 存放 64 位数高 32 位,Rs 存放 64 位数低 32 位,结果保存在两个连续的 GR 中,其中 Rd+1 存放 64 位结果高 32 位,Rd 存放 64 位结果低 32 位。随着值的移位,最高有效位被符号扩展,最后移出的低位存储在进位标志位中。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR, 且 Rd、Rs 必须为偶数

#### 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} >>> GR[Rt]$   $CF = \{GR[Rs+1], GR[Rs]\}_{GR[Rt]-1}$

#### 异常:

#### 备注:

Rd 用 0 槽寄存器写入通路, Rd+1 使用 1 槽寄存器写入通路。

当 Rt=0 时, CF 设置为 0

#### 4.7.10. SL64

内核: v1

#### 格式:

SL64 Rd, Rs, Rt

#### 目的:

将 64 位源操作数进行逻辑左移指定位。

#### 描述:

将 Rs+1, Rs 中的 64 位源操作数进行逻辑左移 Rt 寄存器低 6 位指定的量,其中 Rs+1 存放 64 位数高 32 位,Rs 存放 64 位数低 32 位,结果保存在两个连续的 GR 中,其中 Rd+1 存放 64 位结果高 32 位,Rd 存放 64 位结果低 32 位。随着值的移位,低位被 0 填充,最后移出的高位存储在进位标志位中。

#### 限制条件:

Rd为GR, Rs为GR, Rt为GR, 且Rd、Rs必须为偶数

#### 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} << GR[Rt]$   $CF = \{GR[Rs+1], GR[Rs]\}_{64\text{-}GR[Rt]}$

#### 异常:

#### 备注:

Rd 用 0 槽寄存器写入通路, Rd+1 使用 1 槽寄存器写入通路。

当 Rt=0 时, CF 设置为 0

#### 4.7.11. SRL64

内核: v1

#### 格式:

SRL64 Rd, Rs, Rt

#### 目的:

将 64 位源操作数进行逻辑右移指定位。

#### 描述:

将 Rs+1-Rs 中的 64 位源操作数进行逻辑右移 Rt 寄存器低 6 位指定的量,其中 Rs+1 存放 64 位数高 32 位, Rs 存放 64 位数低 32 位,结果保存在两个连续的 GR 中,其中 Rd+1 存放 64 位结果高 32 位,Rd 存放 64 位结果低 32 位。随着值的移位,高位被 0 填充,最后移出的低位存储在进位标志位中。

#### 限制条件:

Rd为GR, Rs为GR, Rt为GR, 且Rd、Rs必须为偶数

#### 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} >> GR[Rt]$   $CF = \{GR[Rs+1], GR[Rs]\}_{GR[Rt]-1}$

#### 异常:

#### 备注:

Rd 用 0 槽寄存器写入通路, Rd+1 使用 1 槽寄存器写入通路。

当 Rt=0 时, CF 设置为 0

## 4.7.12. SLI

内核: v2

#### 格式:

SLI Rd, Rs, imm<sub>6</sub>

## 目的:

将一个 32 位数进行左移(空出的低位补零)得到结果,保存低 32 位,最后移出的高位存储在进位标志位中。

#### 描述:

Rd ← Rs << imm<sub>6</sub>

#### 限制条件:

Rd为GR, Rs为GR, imm<sub>6</sub>为6位立即数

## 操作:

temp ← GR[Rs] << imm<sub>6</sub>

$GR[Rd] \leftarrow temp_{31..0}$

$CF = GR[Rs]_{32-imm6}$

## 异常:

.

## 备注:

.

## 4.7.13. SRAI

内核: v2

#### 格式:

SRAI Rd, Rt, imm<sub>6</sub>

#### 目的:

将一个32位数进行算数右移得到结果,最后移出的低位存储在进位标志位中。

#### 描述:

Rd ← Rs >>> imm<sub>6</sub>

空出的高位补符号位

## 限制条件:

Rd为GR,Rs为GR,imm6为6位立即数

## 操作:

$GR[Rd] \leftarrow GR[Rs] >>> imm_6$

$CF = GR[Rs]_{imm6-1}$

## 异常:

;

备注:

:

## 4.7.14. SRLI

内核: v2

格式:

SRLI Rd, Rs, imm<sub>6</sub>

目的:

将一个32位数进行逻辑右移得到结果,最后移出的低位存储在进位标志位中。

## 描述:

Rd ← Rs >> imm<sub>6</sub>

空出的高位补零

## 限制条件:

Rd为GR,Rs为GR,imm6为6位立即数

## 操作:

$GR[Rd] \leftarrow GR[Rs] >> imm_6$

$CF = GR[Rs]_{imm6-1}$

异常:

;

备注:

## 4.8. 标量运算指令 - 比特位域指令

#### **4.8.1. BFEXT**

内核: v1

格式:

BFEXT Rd, Rs, imm0, imm1

目的:

比特域位提取。Rs 中的某一段比特域提取并保存

#### 描述:

将 Rs 从 imm0 + imm1 - 1 位置开始(imm0 表示最低位置),宽度为 imm1 的比特域提取出来,高位进行符号扩展后存放在 Rd 中。\_\_\_\_\_

比特域提取后符号扩展至 32 位送入 Rd。实现指令功能时:

- (1) 需要的 mask 为 11111111110....0 (比特域位置为 0)

- (2) 生成 mask: ~(1 << imm1 1) FFFFFF...FF << imm1

- (3) Rs 右移 imm0

- (4) 根据 Rs[imm1-1]的值决定是 Rs | mask 还是 Rs & ~mask (高位补充符号位)

#### 限制条件:

Rd 为 GR, Rs 为 GR, imm0, imm1 均为 5 位立即数

#### 操作:

$GR[Rd] \leftarrow sign\_extend (GR[Rs]_{(imm0 + imm1 - 1) ... imm0})$

异常:

备注:

#### **4.8.2. BFEXTU**

内核: v1

#### 格式:

BFEXTU Rd, Rs, imm0, imm1

#### 目的:

比特域位提取。Rs中的某一段比特域提取并保存

#### 描述:

将 Rs 从 imm0 + imm1 - 1 位置开始(imm0 表示最低位置),宽度为 imm1 的比特域提取出来,高位进行零扩展后存放在 Rd 中。

比特域提取后符号扩展至 32 位送入 Rd。实现指令功能时:

- (1) 需要的 mask 为 00000001....1 (比特域位置为 1)

- (2) 生成 mask: (1 << imm1 1)~( FFFFFF...FF << imm1)

- (3) Rs 逻辑右移 imm0

- (4) 提取比特域: Rs & mask (高位为零,低位为提取的比特域)

#### 限制条件:

Rd 为 GR, Rs 为 GR, imm0, imm1 均为 5 位立即数

#### 操作:

$GR[Rd] \leftarrow zero\_extend (GR[Rs]_{(imm0 + imm1 - 1)...imm0})$

#### 异常:

:

#### 备注:

#### 4.8.3. **BFST**

内核: v1

#### 格式:

BFST Rd, Rs, imm0, imm1

#### 目的:

比特域位设置。Rd 中的某一段比特域设置成给定值 Rs

#### 描述:

将 Rd 从 imm0 + imm1 - 1 位置开始(imm0 表示最低位置),宽度为 imm1 的比特域设置成 Rs 的低 imm1 位。实现指令功能时:

- (1) 需要的 mask 为 11111111110....0 (比特域位置为 0)

- (2) 生成 mask : ~(1 << imm1 1) FFFFFF...FF << imm1

- (3)目标域清空: Rd & ((mask << imm0) | ~mask2), (目标域置 0, 别忘了低位要保持原来的值)

- (4) Rs 移位至目标位置: (Rs & ~mask) << imm0

- (5) 目标域设置: Rd | Rs

#### 限制条件:

Rd 为 GR, Rs 为 GR, imm0, imm1 均为 5 位立即数

#### 操作:

$GR[Rd]_{(imm0+imm1-1)...imm0} \leftarrow GR[Rs]_{(imm1-1)..0}$

#### 异常:

;

#### 备注:

## 4.8.4. BST

内核: v1

格式:

BST Rd, imm<sub>5</sub>

目的:

设置比特位。Rd 第 imm 位置 1

描述:

Rd<sub>imm</sub>=1 (最低位定义为第0位)

限制条件:

Rd为GR,imm为5位立即数

操作:

GR[Rd]<sub>imm</sub> ← 1

异常:

;

备注:

## 4.8.5. BCLR

内核: v1

格式:

BCLR Rd, imm<sub>5</sub>

目的:

清空比特位设置。Rd 第 imm 位置 0

描述:

Rd<sub>imm</sub> = 0 (最低位定义为第 0 位)

限制条件:

Rd为GR,imm为5位立即数

操作:

GR[Rd]<sub>imm</sub> ← 0

异常:

;

备注:

# 5. FPU 指令

## 5.1. 运算指令

#### **5.1.1. FSMUL**

内核: v1

格式:

FSMUL Rd, Rs, Rt

目的:

标量单精度浮点数乘法

#### 描述:

Rs 的 32 位单精度浮点数为乘数, Rt 的 32 位单精度浮点数为被乘数,按 IEEE 754 标准执行单精度浮点乘法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为0或者1来判断是否+1)后写入 Rd。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

$GR[Rd] \leftarrow GR[Rs] * GR[Rt]$

#### 异常:

#### **5.1.2. FSMAC**

内核: v1

格式:

FSMAC Rd, Rs, Rt

目的:

标量单精度浮点数乘累加

#### 描述:

Rs 的 32 位单精度浮点数为乘数,Rt 的 32 位单精度浮点数为被乘数,Rd 的 32 位单精度浮点数为累加数,按 IEEE 754 标准执行单精度浮点乘法后再加上累加数,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入 Rd。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

操作:

$GR[Rd] \leftarrow GR[Rs] * GR[Rt] + GR[Rd]$

异常:

#### **5.1.3. FSEINV**

内核: v1

格式:

FSEINV Rd, Rs

目的:

标量单精度浮点数倒数逼近

#### 描述:

对 Rs 的 32 位单精度浮点数执行倒数查表操作。对于尾数部分,基于 ROM 构成一张 256 项、每项 8bit 的查找表。取 Rs [22:15]作为索引,根据索引值到 ROM 查找表中读出相应的 8bit 数据作为结果尾数的高 8 位,在其后添加 15 个 0 作为尾数中间结果。

对于指数部分,将 Rs 的指数部分进行右移一位操作,得到指数的中间结果。

将符号位、尾数、指数部分进行拼接和规格化操作,得到32bit结果存放在Rd中。

#### 限制条件:

Rd为GR,Rs为GR

#### 操作:

W ← GR[Rs]<sub>22..15</sub>

Temp\_fraction  $\leftarrow$  {ROM<sub>W+7..W</sub>, 15'b0}

Temp\_exp ← 8'd255 + GR[Rs] 30..23

Temp\_signal ← GR[Rs] 31

GR[Rd] ← normalization{ Temp fraction, Temp exp, Temp signal}

#### 异常:

### 5.1.4. FSEISQRT

内核: v1

格式:

FSEISQRT Rd, Rs

目的:

标量单精度浮点数倒数平方根逼近

#### 描述:

对 Rs 的 32 位单精度浮点数执行倒数平方根查表操作。根据指数部分奇偶性对尾数部分进行移位,指数为偶数时尾数不动,指数为奇数时尾数向右移动一位,指数加一。

对于尾数部分,基于 ROM 构成一张 256 项、每项 8bit 的查找表。取 Rs [22:15]作为索引,根据索引值到 ROM 查找表中读出相应的 8bit 数据作为结果尾数的高 8 位,在其后添加 15 个 0 作为尾数中间结果。

对于指数部分,将 Rs 的指数部分进行取反操作,得到指数的中间结果。

将符号位、尾数、指数部分进行拼接和规格化操作,得到32bit结果存放在Rd中

### 限制条件:

Rd 为 GR, Rs 为 GR

#### 操作:

$W \leftarrow GR[Rs]_{23}? GR[Rs]_{22..15}: GR[Rs]_{22..15} >> 1$

Temp fraction  $\leftarrow$  {ROM<sub>W+7..W</sub>, 15'b0}

Temp exp  $\leftarrow$  ((GR[Rs] 30..23 +GR[Rs] 23 ? 0 : 1)-8'd255) >> 1 + 8'd255

Temp\_signal ← GR[Rs] 31

GR[Rd] ← normalization{ Temp\_fraction , Temp\_exp, Temp\_signal}

#### 异常:

#### 5.1.5. FSDIV

内核: v1

格式:

FSDIV Rd, Rs, Rt

目的:

标量单精度浮点数除法

#### 描述:

Rs 的 32 位单精度浮点数为被除数, Rt 的 32 位单精度浮点数为除数,按 IEEE 754 标准执行单精度浮点除法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为0或者1来判断是否+1)后写入 Rd。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

操作:

$GR[Rd] \leftarrow GR[Rs] / GR[Rt]$

异常:

# **5.1.6. FSSQRT**

内核: v1

格式:

FSSQRT Rd, Rs

目的:

标量单精度浮点数开方根

# 描述:

对 Rs 的 32 位单精度浮点数执行开方根运算,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入 Rd。

#### 限制条件:

Rd为GR,Rs为GR

操作:

GR[Rd] ← SquareRoot(GR[Rs])

异常:

#### **5.1.7. FSADD**

内核: v1

格式:

FSADD Rd, Rs, Rt

目的:

标量浮点单精度加法

#### 描述:

Rs 和 Rd 的 32 位单精度浮点数分别作为两个源操作数,按 IEEE 754 标准执行单精度浮点加法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1) 后写入 Rd。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

操作:

$GR[Rd] \leftarrow GR[Rs] + GR[Rt]$

异常:

备注:

### **5.1.8. FSSUB**

内核: v1

格式:

FSSUB Rd, Rs, Rt

目的:

标量浮点单精度减法

#### 描述:

Rs 的 32 位单精度浮点数为被减数,Rt 的 32 位单精度浮点数为减数,按 IEEE 754 标准执行单精度浮点减法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入 Rd。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

操作:

$GR[Rd] \leftarrow GR[Rs] - GR[Rt]$

异常:

备注:

# **5.1.9. FSABS**

内核: v1

格式:

FSABS Rd, Rs

目的:

标量浮点单精度取绝对值

# 描述:

对 Rs 的 32 位单精度浮点数执行取绝对值操作,结果写入 Rd。

#### 限制条件:

Rd为GR, Rs为GR, Rt为GR

操作:

GR[Rd] ← ABS(GR[Rs])

异常:

备注:

# 5.1.10. FSMAX

内核: v1

格式:

FSMAX Rd, Rs, Rt

目的:

标量浮点单精度数据取较大值

# 描述:

Rs 的 32 位单精度浮点数值和 Rt 的 32 位单精度浮点数值分别作为两个源操作数,取两者中较大的一个写入 Rd。

### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

# 操作:

$GR[Rd] \leftarrow GR[Rs] > GR[Rt] ? GR[Rs] : GR[Rt]$

异常:

# **5.1.11. FSMIN**

内核: v1

格式:

FSMIN Rd, Rs, Rt

目的:

标量浮点单精度数据取较小值

# 描述:

Rs 的 32 位单精度浮点数值和 Rt 的 32 位单精度浮点数值分别作为两个源操作数,取两者中较小的一个写入 Rd。

# 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

# 操作:

$GR[Rd] \leftarrow GR[Rs] < GR[Rt] ? GR[Rs] : GR[Rt]$

异常:

### 5.1.12. FDMUL

内核: v3

#### 格式:

FDMUL Rd, Rs, Rt

#### 目的:

标量双精度浮点数乘法

#### 描述:

{Rs+1, Rs}的 64 位双精度浮点数为乘数,{Rt+1, Rt}的 64 位双精度浮点数为被乘数,按 IEEE 754 标准执行双精度浮点乘法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入{Rd+1, Rd}。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

{GR[Rd+1], GR[Rd]} ← {GR[Rs+1], GR[Rs]} \* {GR[Rt+1], GR[Rt]}

### 异常:

#### 5.1.13. FDMAC

内核: v3

#### 格式:

FDMAC Rd, Rs, Rt

#### 目的:

标量双精度浮点数乘累加

#### 描述:

{Rs+1, Rs}的 64 位双精度浮点数为乘数,{Rt+1, Rt}的 64 位双精度浮点数为被乘数,{Rd+1, Rd}的 64 位双精度浮点数为累加数,按IEEE 754 标准执行双精度浮点乘法后再加上累加数,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入{Rd+1, Rd}。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

#### 操作:

{GR[Rd+1], GR[Rd]} ← {GR[Rs+1], GR[Rs]} \* {GR[Rt+1], GR[Rt]} + {GR[Rd+1], GR[Rd]}

#### 异常:

#### 5.1.14. FDADD

内核: v3

格式:

FDADD Rd, Rs, Rt

目的:

标量浮点双精度加法

#### 描述:

{Rs+1, Rs}和{Rt+1, Rt}的 64 位双精度浮点数分别作为两个源操作数,按 IEEE 754 标准执行双精度浮点加法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入{Rd+1, Rd}。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} + \{GR[Rt+1], GR[Rt]\}$

异常:

备注:

#### 5.1.15. FDSUB

内核: v3

格式:

FDSUB Rd, Rs, Rt

目的:

标量浮点双精度减法

#### 描述:

{Rs+1, Rs}的 64 位双精度浮点数为被减数,{Rt+1, Rt}的 64 位双精度浮点数为减数,按 IEEE 754 标准执行双精度浮点减法,并对结果进行规格化处理(包含舍入操作,根据移出或截断的最高位为 0 或者 1 来判断是否+1)后写入{Rd+1, Rd}。

#### 限制条件:

Rd为GR,Rs为GR,Rt为GR

#### 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} - \{GR[Rt+1], GR[Rt]\}$

异常:

备注:

# **5.1.16. FDABS**

内核: v3

格式:

FDABS Rd, Rs

目的:

标量浮点单精度取绝对值

# 描述:

对{Rs+1, Rs}的 64 位双精度浮点数执行取绝对值操作,结果写入{Rd+1, Rd}。

# 限制条件:

Rd 为 GR, Rs 为 GR

# 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow ABS(\{GR[Rs+1], GR[Rs]\})$

异常:

备注:

#### 5.1.17. FDMAX

内核: v3

格式:

FDMAX Rd, Rs, Rt

目的:

标量浮点双精度数据取较大值

#### 描述:

{Rs+1, Rs}的 64 位双精度浮点数值和{Rt+1, Rt}的 64 位双精度浮点数值分别作为两个源操作数,取两者中较大的一个写入{Rd+1, Rd}。

### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

# 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} > \{GR[Rt+1], GR[Rt]\} ? \{GR[Rs+1], GR[Rs]\} : \{GR[Rt+1], GR[Rt]\}$

异常:

#### **5.1.18. FDMIN**

内核: v3

#### 格式:

FDMIN Rd, Rs, Rt

### 目的:

标量浮点双精度数据取较小值

#### 描述:

{Rs+1, Rs}的 64 位双精度浮点数值和{Rt+1, Rt}的 64 位双精度浮点数值分别作为两个源操作数,取两者中较小的一个写入{Rd+1, Rd}。

#### 限制条件:

Rd 为 GR, Rs 为 GR, Rt 为 GR

# 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow \{GR[Rs+1], GR[Rs]\} < \{GR[Rt+1], GR[Rt]\}? \{GR[Rs+1], GR[Rs]\} : \{GR[Rt+1], GR[Rt]\}$

#### 异常:

# 5.2. 比较指令

# **5.2.1. FSEQ**

内核: v1

格式:

FSEQ Rs, Rt

目的:

标量浮点单精度数据比较(相等)

#### 描述:

若两个单精度浮点数相等,则相应 CON 设置为 1,否则设置为 0

# 限制条件:

Rs 为 GR,Rt 为 GR

# 操作:

IF GR[Rs] == GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

# **5.2.2. FSGT**

内核: v1

格式:

FSGT Rs, Rt

目的:

标量浮点单精度数据比较(大于)

# 描述:

若 Rs 的 32 位单精度浮点数值大于 Rt 的 32 位单精度浮点数值,则相应 CON 设置为 1, 否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

$\mathsf{IF}\;\mathsf{GR}[\mathsf{Rs}] > \mathsf{GR}[\mathsf{Rt}]$

CON = 1;

ELSE

CON = 0;

异常:

# 5.2.3. FSLT

内核: v1

格式:

FSLT Rs, Rt

目的:

标量浮点单精度数据比较(小于)

# 描述:

若 Rs 的 32 位双精度浮点数值小于 Rt 的 32 位单精度浮点数值,则相应 CON 设置为 1, 否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

IF GR[Rs] < GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

#### **5.2.4. FSGE**

内核: v1

格式:

FSGE Rs, Rt

目的:

标量浮点单精度数据比较(大于等于)

# 描述:

若 Rs 的 32 位单精度浮点数值大于等于 Rt 的 32 位单精度浮点数值,则相应 CON 设置为

1, 否则设置为0

# 限制条件:

Rs为GR,Rt为GR

# 操作:

IF GR[Rs] >= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

# 5.2.5. FSLE

内核: v1

格式:

FSLE Rs, Rt

目的:

标量浮点单精度数据比较(小于等于)

# 描述:

若 Rs 的 32 位单精度浮点数值小于等于 Rt 的 32 位单精度浮点数值,则相应 CON 设置为

1, 否则设置为0

# 限制条件:

Rs为GR,Rt为GR

# 操作:

IF GR[Rs] <= GR[Rt]

CON = 1;

ELSE

CON = 0;

异常:

# **5.2.6. FDEQ**

内核: v3

格式:

FDEQ Rs, Rt

目的:

标量浮点双精度数据比较(相等)

# 描述:

若两个双精度浮点数相等,则相应 CON 设置为 1,否则设置为 0

#### 限制条件:

Rs 为 GR,Rt 为 GR

# 操作:

$\mathsf{IF} \{\mathsf{GR}[\mathsf{Rs}+1], \mathsf{GR}[\mathsf{Rs}]\} == \{\mathsf{GR}[\mathsf{Rt}+1], \mathsf{GR}[\mathsf{Rt}]\}$

CON = 1;

ELSE

CON = 0;

异常:

# **5.2.7. FDGT**

内核: v3

格式:

FDGT Rs, Rt

目的:

标量浮点双精度数据比较(大于)

# 描述:

若 $\{Rs+1,Rs\}$ 的 64 位双精度浮点数值大于 $\{Rt+1,Rt\}$ 的 64 位双精度浮点数值,则相应 CON 设置为 1,否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

IF  $\{GR[Rs+1], GR[Rs]\} > \{GR[Rt+1], GR[Rt]\}$

CON = 1;

**ELSE**

CON = 0;

异常:

# 5.2.8. FDLT

内核: v3

格式:

FDLT Rs, Rt

目的:

标量浮点双精度数据比较(小于)

# 描述:

若 $\{Rs+1,Rs\}$ 的 64 位双精度浮点数值小于 $\{Rt+1,Rt\}$ 的 64 位双精度浮点数值,则相应 CON 设置为 1,否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

IF  $\{GR[Rs+1], GR[Rs]\} < \{GR[Rt+1], GR[Rt]\}$

CON = 1;

**ELSE**

CON = 0;

异常:

# **5.2.9. FDGE**

内核: v3

格式:

FDGE Rs, Rt

目的:

标量浮点双精度数据比较(大于等于)

# 描述:

若{Rs+1, Rs}的 64 位双精度浮点数值大于等于{Rt+1, Rt}的 64 位双精度浮点数值,则相应 CON 设置为 1, 否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

$\mathsf{IF} \; \{\mathsf{GR}[\mathsf{Rs+1}], \, \mathsf{GR}[\mathsf{Rs}]\} >= \{\mathsf{GR}[\mathsf{Rt+1}], \, \mathsf{GR}[\mathsf{Rt}]\}$

CON = 1;

ELSE

CON = 0;

异常:

# **5.2.10.** FDLE

内核: v3

格式:

FDLE Rs, Rt

目的:

标量浮点双精度数据比较(小于等于)

# 描述:

若{Rs+1, Rs}的 64 位双精度浮点数值小于等于{Rt+1, Rt}的 64 位双精度浮点数值,则相应 CON 设置为 1, 否则设置为 0

# 限制条件:

Rs 为 GR, Rt 为 GR

# 操作:

$\mathsf{IF} \; \{\mathsf{GR}[\mathsf{Rs+1}], \, \mathsf{GR}[\mathsf{Rs}]\} \mathrel{<=} \{\mathsf{GR}[\mathsf{Rt+1}], \, \mathsf{GR}[\mathsf{Rt}]\}$

CON = 1;

ELSE

CON = 0;

异常:

# 5.3. 类型转换指令

# **5.3.1. FCVTSF**

内核: v1

格式:

FCVTSF Rd, Rs

目的:

标量浮点单精度转有符号整型

描述:

Rs 的 32 位单精度浮点数值转换为 32 位有符号整型数后写入 Rd 中。

限制条件:

Rd为GR,Rs为GR

操作:

GR[Rd] ← SingleToSignedInt (GR[Rs])

异常:

# **5.3.2. FCVTFS**

内核: v1

格式:

FCVTFS Rd, Rs

目的:

标量有符号整型转浮点单精度

描述:

Rs 的 32 位有符号整型数值转换为 32 位单精度浮点数后写入 Rd 中。

限制条件:

Rd 为 GR,Rs 为 GR

操作:

GR[Rd] ← SignedIntToSingle (GR[Rs])

异常:

# **5.3.3. FCVTSU**

内核: v1

格式:

FCVTSU Rd, Rs

目的:

标量浮点单精度转无符号整型

描述:

Rs 的 32 位单精度浮点数值转换为 32 位无符号整型数后写入 Rd 中。

限制条件:

Rd 为 GR, Rs 为 GR

操作:

GR[Rd] ← SingleToUnsignedInt (GR[Rs])

异常:

# **5.3.4. FCVTUS**

内核: v1

格式:

FCVTUS Rd, Rs

目的:

标量无符号整型转浮点单精度

描述:

Rs 的 32 位无符号整型数值转换为 32 位单精度浮点数后写入 Rd 中。

限制条件:

Rd 为 GR,Rs 为 GR

操作:

GR[Rd] ← UnsignedIntToSingle (GR[Rs])

异常:

# **5.3.5. FCVTDF**

内核: v3

格式:

FCVTDF Rd, Rs

目的:

标量浮点双精度转有符号整型

描述:

{Rs+1, Rs}的 64 位双精度浮点数值转换为 32 位有符号整型数后写入 Rd 中。

限制条件:

Rd 为 GR,Rs 为 GR

操作:

GR[Rd] ← DoubleToSignedInt ({GR[Rs+1], GR[Rs]))

异常:

# **5.3.6. FCVTFD**

内核: v3

格式:

FCVTFD Rd, Rs

目的:

标量有符号整型转浮点双精度

# 描述:

Rs 的 32 位有符号整型数值转换为 64 位双精度浮点数后写入{Rd+1, Rd}中。

#### 限制条件:

Rd 为 GR, Rs 为 GR

# 操作:

$\{GR[Rd+1], GR[Rd]\} \leftarrow SignedIntToDouble (GR[Rs])$

异常:

# **5.3.7. FCVTDU**

内核: v3

格式:

FCVTDU Rd, Rs

目的:

标量浮点双精度转无符号整型

描述:

{Rs+1, Rs}的 64 位双精度浮点数值转换为 32 位无符号整型数后写入 Rd 中。

限制条件:

Rd 为 GR,Rs 为 GR

操作:

GR[Rd] ← DoubleToUnsignedInt ({GR[Rs+1], GR[Rs]))

异常:

# **5.3.8. FCVTUD**

内核: v3

格式:

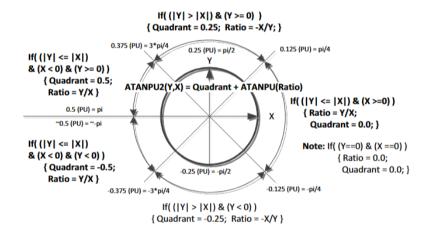

FCVTUD Rd, Rs